# Lecture Notes in Computer Science

4523

Commenced Publication in 1973

Founding and Former Series Editors:

Gerhard Goos, Juris Hartmanis, and Jan van Leeuwen

#### **Editorial Board**

David Hutchison

Lancaster University, UK

Takeo Kanade

Carnegie Mellon University, Pittsburgh, PA, USA

Josef Kittler

University of Surrey, Guildford, UK

Jon M. Kleinberg

Cornell University, Ithaca, NY, USA

Friedemann Mattern

ETH Zurich, Switzerland

John C. Mitchell

Stanford University, CA, USA

Moni Naor

Weizmann Institute of Science, Rehovot, Israel

Oscar Nierstrasz

University of Bern, Switzerland

C. Pandu Rangan

Indian Institute of Technology, Madras, India

Bernhard Steffen

*University of Dortmund, Germany*

Madhu Sudan

Massachusetts Institute of Technology, MA, USA

Demetri Terzopoulos

University of California, Los Angeles, CA, USA

Doug Tygar

University of California, Berkeley, CA, USA

Moshe Y. Vardi

Rice University, Houston, TX, USA

Gerhard Weikum

Max-Planck Institute of Computer Science, Saarbruecken, Germany

Yann-Hang Lee Heung-Nam Kim Jong Kim Yongwan Park Laurence T. Yang Sung Won Kim (Eds.)

# Embedded Software and Systems

Third International Conference, ICESS 2007 Daegu, Korea, May 14-16, 2007 Proceedings

#### Volume Editors

Yann-Hang Lee

Arizona State University, Department of Computer Science and Engineering 699 S. Mill Av., Tempe, AZ 85287, USA

E-mail: yhlee@asu.edu

Heung-Nam Kim

Embedded S/W Research Division 161

Gajeong-Dong, Yuseong-Gu, Daejeon, 305-700, Korea

E-mail: hnkim@etri.re.kr

Jong Kim

Pohang University of Science and Technology

Department of Computer Science and Engineering (POSTECH)

San 31, Hyoja-dong, Nam-gu, Pohang 790-784, Korea

E-mail: jkim@postech.ac.kr

Yongwan Park

Sung Won Kim

Yeungnam University, School of Electrical Engineering and Computer Science

214-1 Dae-Dong, Gyeongsan City, Gyeongbuk, 712-749, Korea

E-mail: {ywpark, swon}@yu.ac.kr

Laurence T. Yang

St. Francis Xavier University, Department of Computer Science

Antigonish, NS, B2G 2W5, Canada

E-mail: lyang@stfx.ca

Library of Congress Control Number: 2007926910

CR Subject Classification (1998): C.3, C.2, C.5.3, D.2, D.4, H.4

LNCS Sublibrary: SL 2 – Programming and Software Engineering

ISSN 0302-9743

ISBN-10 3-540-72684-5 Springer Berlin Heidelberg New YorkISBN-13 978-3-540-72684-5 Springer Berlin Heidelberg New York

This work is subject to copyright. All rights are reserved, whether the whole or part of the material is concerned, specifically the rights of translation, reprinting, re-use of illustrations, recitation, broadcasting, reproduction on microfilms or in any other way, and storage in data banks. Duplication of this publication or parts thereof is permitted only under the provisions of the German Copyright Law of September 9, 1965, in its current version, and permission for use must always be obtained from Springer. Violations are liable to prosecution under the German Copyright Law.

Springer is a part of Springer Science+Business Media

springer.com

© Springer-Verlag Berlin Heidelberg 2007 Printed in Germany

Typesetting: Camera-ready by author, data conversion by Scientific Publishing Services, Chennai, India Printed on acid-free paper SPIN: 12068289 06/3180 5 4 3 2 1 0

# **Preface**

Embedded systems, i.e., computers inside products, have been adopted widely in many domains, including traditional control systems, medical instruments, wired and wireless communication devices, aerospace equipment, human-computer interfaces, and sensor networks. Two significant trends have recently been observed due to the increasing computation power and communication bandwidth. The first is that embedded systems are getting connected and are cooperating as distributed systems. The other is the extensive software in middleware and embedded applications. These trends are apparent in academic and industrial research and in the papers submitted to the International Conference on Embedded Software and Systems.

The 3rd International Conference on Embedded Software and Systems (ICESS 2007), to be held in Daegu, Republic of Korea, on May 14-16, aims to advance embedded software and systems research, development, and design competence, and to enhance international communication and collaboration. It consists of the traditional core area of embedded systems infrastructure in architecture, software, hardware, real-time computing, and testing and verification, as well as additional areas of special emphasis: pervasive/ubiquitous computing and sensor networks, HW/SW co-design and SoC, wireless communications, power-aware computing, security and dependability, and multimedia and HCI. In addition, tutorial sessions on the broad fields of embedded computing, a panel discussion session and keynote addresses are included in the conference. Based on the 387 submitted manuscripts and the 77 accepted papers, we expect that the forum will be full of high quality presentations and productive discussions.

ICESS 2007 has been made possible by the hard work of a number of people, to whom we are very grateful. They include the members of the organization committees and the vice chairs of the technical tracks in the technical program committee. Recognition is warranted for the commendable job of all members of the technical program committee, who, in the short paper reviewing period, have accomplished the significant workload of evaluating, on average, 9 papers and providing constructive comments.

We are particularly thankful to Laurence T. Yang for his guidance and effort in continuing the ICESS series. In addition, we thank all authors who submitted their outstanding work; without them the conference would not have been possible. Finally, we gratefully acknowledge the support from our sponsors.

April 2007

Yann-Hang Lee and Heung Nam Kim

# Organization

# **Organizers**

ICESS-07 was organized by the Institute of Embedded Engineering of Korea (IEMEK).

# **Sponsors**

Daegu GyeoungBuk Institute of Science & Technology (DGIST), Korea Embedded Technology Education Center (EmTEC), New University for Regional Innovation (NURI), Korea

ETNEWS, Korea

Daegu Digital Industry Promotion agency (DIP), Korea R&DB Center for Embedded System Industry, Korea The Federation of Korea Information Industries, Korea

SK Telecom, Korea SAMSUNG, Korea

DAEGU Convention & Visitors Bureau, Korea

Gyeongsangbuk-Do, Korea

Lecture Notes in Computer Science (LNCS), Springer

#### **Executive Committee**

General Chairs Kyu-Suk Chung, President of IEMEK and DGIST,

Korea

Peter Marwedel, University of Dortmund and ICD,

Germany

Program Chairs Yann-Hang Lee, Arizona State University, USA

Heung Nam Kim, ETRI, Korea

Steering Chairs Zhaohui Wu, Zhejiang University, China

Laurence T. Yang, St. Francis Xavier University,

Canada

Program Vice-Chairs Zonghua Gu, Hong Kong University of Science and

Technology, Hong Kong, China

Kenneth Ricks, The University of Alabama, USA Chanik Park, Pohang University of Science and

Technology, Korea

Byoungchul Ahn, YeungNam University, Korea

Seong-dong Kim, ETRI, Korea

Karam Chatha, Arizona State University, USA

Mohamed Younis, University of Maryland

Baltimore County, USA

Christian W. Probst, Technical University of

Denmark, Denmark

Farn Wong, National Taiwan University, Taiwan

Liudong Xing, University of

Massachusetts - Dartmouth, USA

Sangwook Kim, Kyungpook National University,

Korea

Publicity Chairs Young Jin Nam, Daegu University, Korea

Wei Zhang, Southern Illinois University, USA Yu Hua, HuaZhong University of Science and

Technology, China

Yongxin Zhu, Shanghai Jiaotong University, China

Publication Chair Sung Won Kim, YeungNam University, Korea

Tony Li Xu, St. Francis Xavier University, Canada

Finance Chair Yongwan Park, Yeungnam University, Korea

Local Chair Dong Ha Lee, DGIST, Korea

Organization Chair Jong Kim, Pohang University of Science and

Technology, Korea

# Program/Technical Committee

Ayman Abdel-Hamid Arab Academy for Science and Technology,

Egypt

Kemal Akkaya Southern Illinois University, USA

Fatih Alagoz Bogazici University, Turkey

Suprasad Amari Relex Software Corporation, USA Kwang-Seon Ahn Kyungpook National University, Korea

Beongku An Hongik University, Korea

Adel Youssef Google, USA

Li Bai Temple University, USA Iain Bate University of York, UK

Jalel Ben-Othman Université de Versailles, France

Elaheh Bozorgzadeh University of California, Irvine, USA

Hasan Cam Arizona State University, USA

Erdal Cayirci University of Stavanger, Norway

Samarjit Chakraborty National University of Singapore, Singapore

Naehyuck Chang Seoul National University, Korea

Changsik Cho ETRI, Korea

Tae-Young Choe Kumoh National Institute of Technology,

Korea

Byung-Jae Choi Daegu University, Korea

Tae Yoon Chung Kangnung National University, Korea Yuanshun Dai Purdue University, Indianapolis, USA

Susan K. Donohue Sameh Elsharkawy Mohammed Ferdjallah Diana Franklin Xinwen Fu Masahiro Fujita Gernot Heiser

Dieter Hogrefe Jerry Hom Seongsoo Hong Harry Hsieh Pao-Ann Hsiung Chung-Hsing Hsu

Yu Hua Huadong Ma

Chung-Yang (Ric) Huang Dijiang Huang Jae Doo Huh Claude Jard Jie-Hong Roland Jiang

Ibrahim Kamel Sooyong Kang Kevin Kassner

Woo Young Jung

SoonKi Jung

Srinivas Katkoori Cheon Shik Kim Daeyoung Kim

Heesun Kim

Jeein Kim

Jeonggon Kim

Moonzoo Kim

Munchurl Kim

Myungchul Kim

Namchul Kim Christos Kloukinas Turgay Korkmaz Ibrahim Korpeoglu Uli Kremer

Kiryong Kwon

University of Virginia, USA

Catholic University of America, USA The University of Tennessee, USA Cal Poly, San Luis Obispo, USA Dakota State University, USA University of Tokyo, Japan

The University of New South Wales, Sydney,

Australia

Universität Göttingen, Germany

Rutgers University, USA

Seoul National University, Korea

University of California, Riverside, USA National Chung Cheng University, Taiwan Los Alamos National Laboratory, USA

HUST, China

Beijing University of Post and Telecommunication, China National Taiwan University, Taiwan

Arizona State University, USA

ETRI, Korea IRISA. France

National Taiwan University, Taiwan Kyungpook National University, Korea Daegu Gyeongbuk Institute of Science and

Technology, Korea Sharjah University, UAE Hanyang University, Korea

Dynetics Corporation, Huntsville, Alabama,

USA

University of Southern Florida, USA

Anyang University, Korea

Information and Communication University,

Korea

Andong National University, Korea

Konkuk University, Korea Hansei University, Korea

KAIST, Korea ICU, Korea

Information and Communications University,

Korea

Kyungpook National University, Korea

City University London, UK

University of Texas at San Antonio, USA

Bilkent University, Turkey Rutgers University, USA

Pukyong National University, Korea

Ben Lee

Bong Gyu Lee

Gangsoo Lee

Insup Lee

Seunghwan Lee

Seungjoon Lee

Xiaolin Li

Huan Li

Xue Liu

Sin Ming Loo

Roman Lysecky

Pyeongsoo Mah

Viswanathan Mahesh

Marc St-Hilaire Nicholas McGuire Abdelhamid Mellouk Leila Meshkat

Ahmed Mostefaoui

Tamer Nadeem

Farid Nait-Abdesselam Sang Yep Nam

Alberto Nannarelli

Yang Ni Hoon Oh

Ossamma Younis Soo Hyun Park Filip Perich Daji Qiao Srivaths Ravi Binoy Ravindran Karim Seada Szili Shao

Chi-Sheng (Daniel) Shih

Oliver Sinnen

Sang H. Son

Christian Steger

William Stapleton

Sooyong Kang

Tarek Bejaoui

Hiroyuki Tomiyama

Damla Turgut

Oregon State University, USA Yonsei University, Korea Hannam University, Korea University of Pennsylvania, USA Samsung Electronics, Korea

ATT Research, USA

Oklahoma State University, USA Beihang University, China McGill University, Canada Boise State University, USA University of Arizona, USA

ETRI, Korea

University of Illinois at

Urbana-Champaign, USA

Carleton University, Canada

Lanzhou University, China

University of Paris XII, France

Jet Propulsion Laboratory, USA

Laboratoire d'Informatique de

Franche-Comté, France

Siemens Corporate Research, USA

University of Lille, France Kyungmoon University, Korea

Technical University of Denmark, Denmark

Intel, USA

Ulsan University, Korea University of Arizona, USA Kookmin University, Korea

Shared Spectrum Company, USA Iowa State University, USA Texas Instruments, India

Virginia Tech, USA Nokia Research, USA

Hong Kong Polytechnic University, China National Taiwan University, Taiwan University of Auckland, New Zealand

University of Virginia, USA

Technical University Graz, Austria The University of Alabama, USA Hanyang University, Korea University of Carthage, Tunisia

Nagoya University, Japan

University of Central Florida, USA

Kuang-Ching Wang Clemson University, USA Shige Wang General Motors, USA

Xiaorui Wang University of Tennessee, USA

Earl Wells The University of Alabama in Huntsville,

USA

Youjip Won Hanyang University, Korea

Woontack Woo GIST, Korea

Haruo Yokoda Tokyo Institute of Technology, Japan

Youngwoo Yoon Yeungnam University, Korea

Adel Youssef Google, USA

Moustafa Youssef University of Maryland College Park, USA

Zhen Yu Iowa State University, USA

Wenhui Zhang Chinese Academy of Sciences, China Wenbing Zhao Cleveland State University, USA

Lin Zhong Rice University, USA

Dakai Zhu University of Texas at San Antonio, USA Yongxin Zhu Shanghai Jiaotong University, China Cliff Zou University of Central Florida, USA Xukai Zou Purdue University, Indianapolis, USA

# **Table of Contents**

| Track 1: Embedded Architecture                                                                       |    |

|------------------------------------------------------------------------------------------------------|----|

| Object-Orientation Is Evil to Mobile Game: Experience from Industrial Mobile RPGs                    | 1  |

| Device-Aware Cache Replacement Algorithm for Heterogeneous Mobile Storage Devices                    | 13 |

| The Lightweight Runtime Engine of the Wireless Internet Platform for Mobile Devices                  | 25 |

| Product Line Based Reuse Methodology for Developing Generic ECU                                      | 37 |

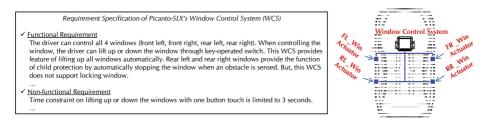

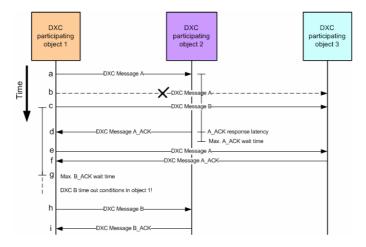

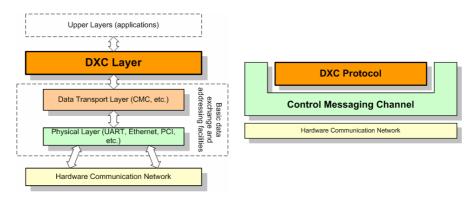

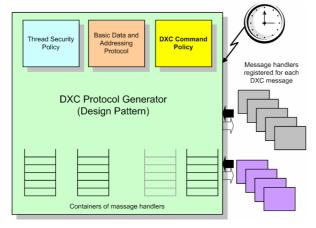

| The Object-Oriented Protocol for Data Exchange and Control in Computational-Diverse Embedded Systems | 46 |

| Track 2: Embedded Hardware                                                                           |    |

| A Link-Load Balanced Low Energy Mapping and Routing for NoC ZhouWenbiao, ZhangYan, and MaoZhigang    | 59 |

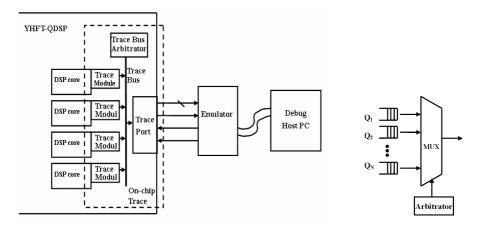

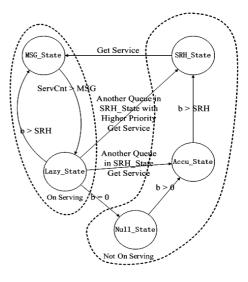

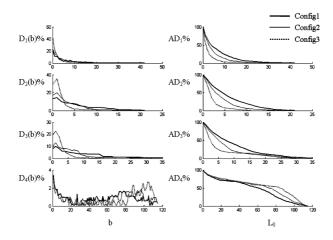

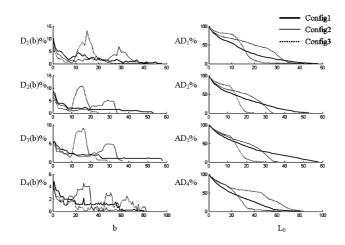

| Scheduling for Combining Traffic of On-Chip Trace Data in Embedded Multi-core Processor              | 67 |

| Memory Offset Assignment for DSPs                                                                    | 80 |

| A Subsection Storage Policy in Intelligent RAID-Based Object Storage Device                          | 88 |

| Joint Source-Channel Decoding ASIP Architecture for Sensor  Networks                                 | 98 |

| Systems                                                                                                           | 109 |

|-------------------------------------------------------------------------------------------------------------------|-----|

| A Design Method for Heterogeneous Adders                                                                          | 121 |

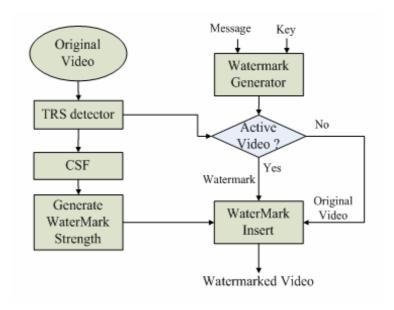

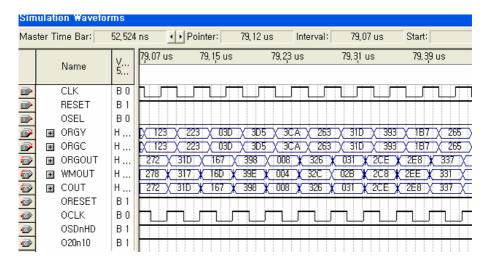

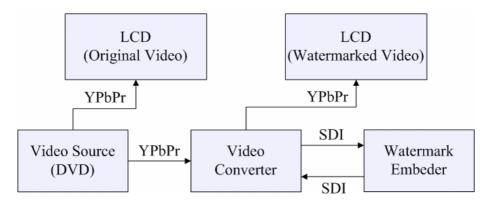

| FPGA Based Implementation of Real-Time Video Watermarking Chip                                                    | 133 |

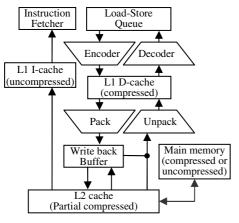

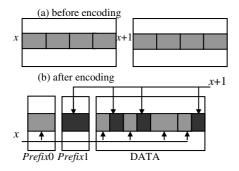

| A Unified Compressed Cache Hierarchy Using Simple Frequent Pattern Compression and Partial Cache Line Prefetching | 142 |

| Track 3: Embedded Software                                                                                        |     |

| Function Inlining in Embedded Systems with Code Size Limitation Xinrong Zhou, Lu Yan, and Johan Lilius            | 154 |

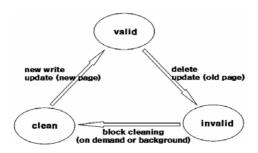

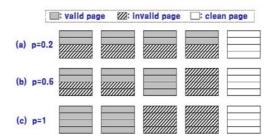

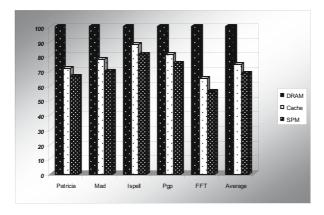

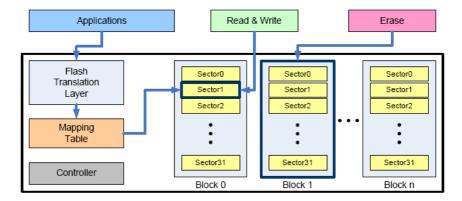

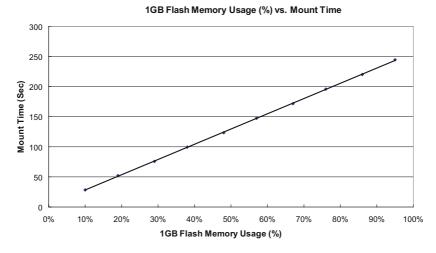

| Performance Characteristics of Flash Memory: Model and Implications                                               | 162 |

| A New Type of Embedded File System Based on SPM                                                                   | 174 |

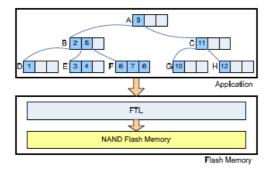

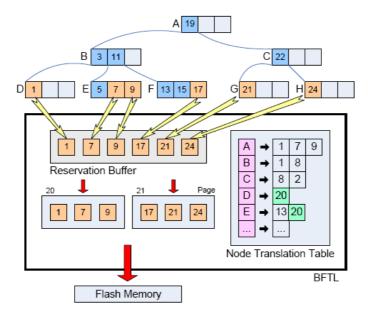

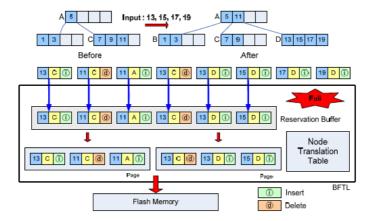

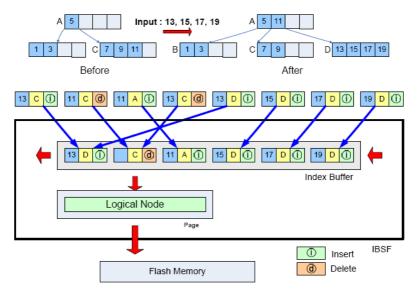

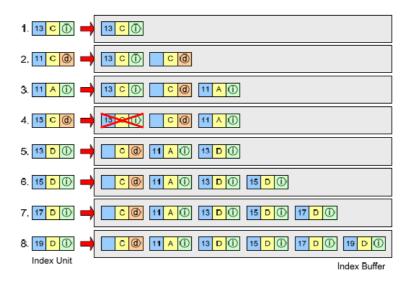

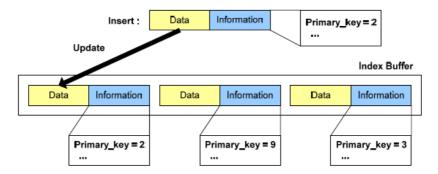

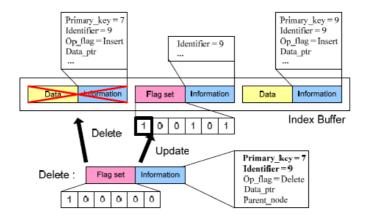

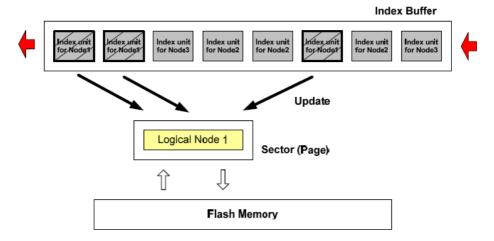

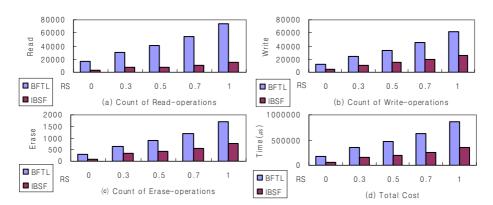

| An Efficient Buffer Management Scheme for Implementing a B-Tree on NAND Flash Memory                              | 181 |

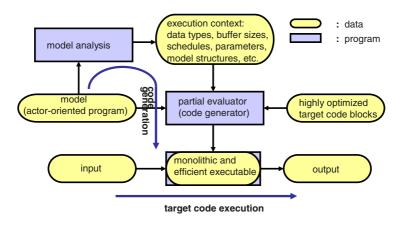

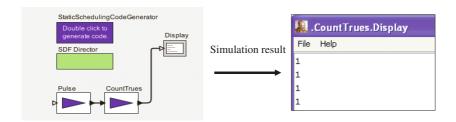

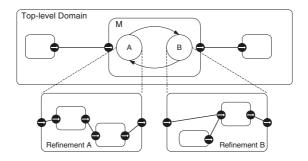

| A Code Generation Framework for Actor-Oriented Models with Partial Evaluation                                     | 193 |

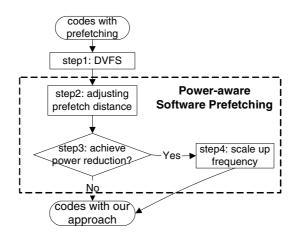

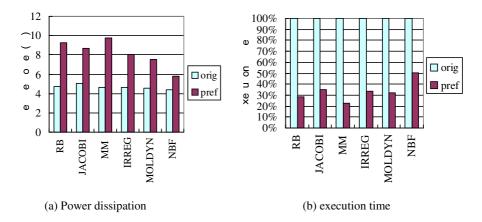

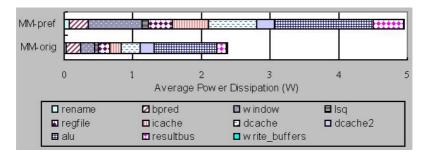

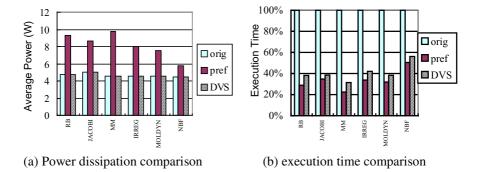

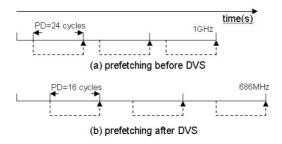

| Power-Aware Software Prefetching                                                                                  | 207 |

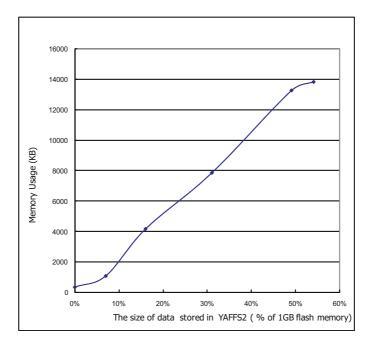

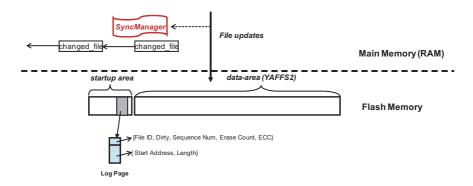

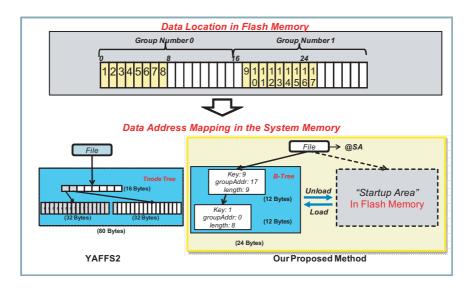

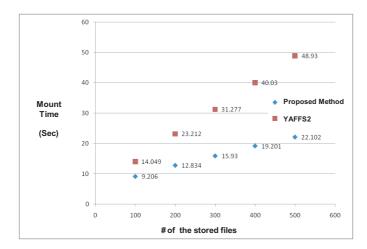

| Fast Initialization and Memory Management Techniques for Log-Based Flash Memory File Systems                      | 219 |

| Track 4: HW-SW Co-design and SoC                                                                                  |     |

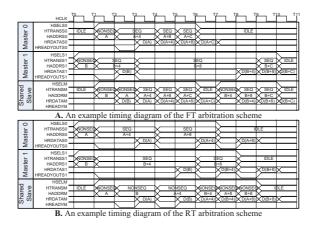

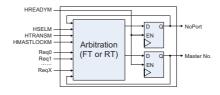

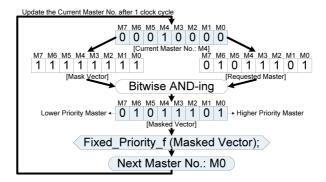

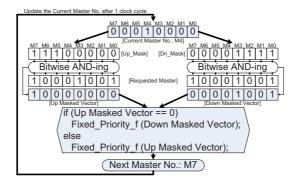

| An Efficient Implementation Method of Arbiter for the ML-AHB Busmatrix                                            | 229 |

Kyung-Ae Cha and Kyungdeok Kim

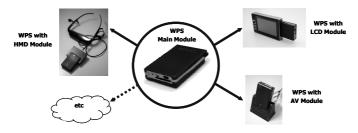

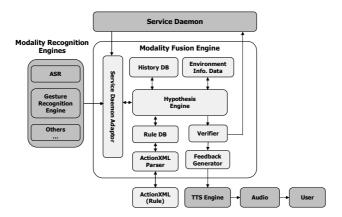

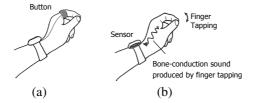

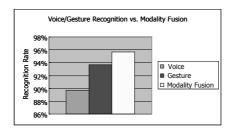

| A Distributed Wearable System Based on Multimodal Fusion                                                                       | 369 |

|--------------------------------------------------------------------------------------------------------------------------------|-----|

| Track 6: Pervasive/Ubiquitos Computing and Sensor Network:                                                                     |     |

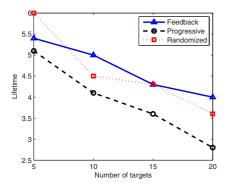

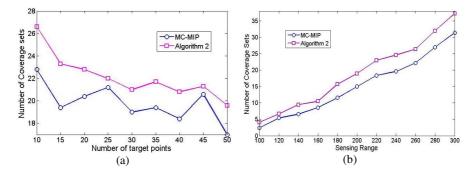

| Randomized Approach for Target Coverage Scheduling in Directional Sensor Network                                               | 379 |

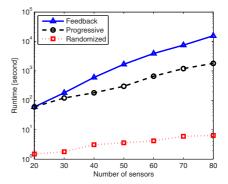

| Efficient Time Triggered Query Processing in Wireless Sensor Networks                                                          | 391 |

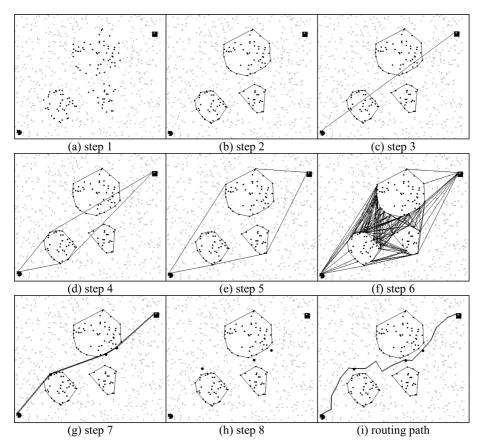

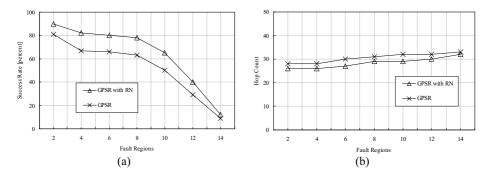

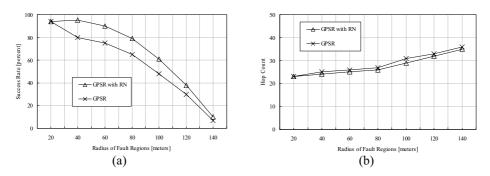

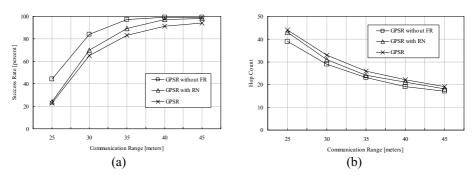

| Dependable Geographical Routing on Wireless Sensor Networks  Yue-Shan Chang, Ming-Tsung Hsu, Hsu-Hang Liu, and Tong-Ying Juang | 403 |

| Minimization of the Redundant Coverage for Dense Wireless Sensor<br>Networks                                                   | 415 |

| Track 7: Power-Aware Computing                                                                                                 |     |

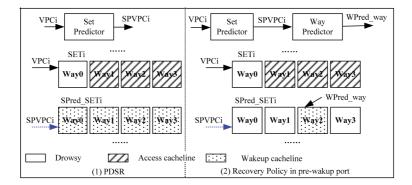

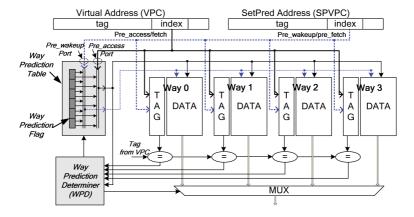

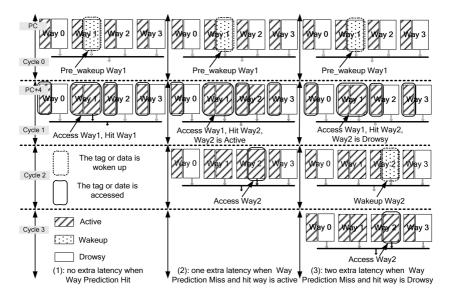

| Improved Way Prediction Policy for Low-Energy Instruction Caches Zhou Hongwei, Zhang Chengyi, and Zhang Mingxuan               | 425 |

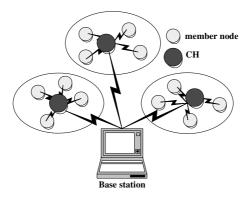

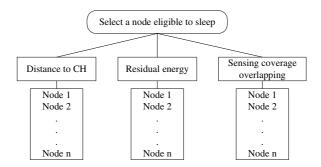

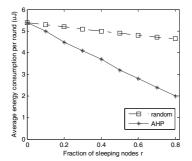

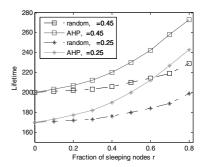

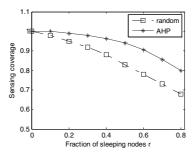

| Sleep Nodes Scheduling in Cluster-Based Heterogeneous Sensor<br>Networks Using AHP                                             | 437 |

| Energy-Efficient Medium Access Control for Wireless Sensor<br>Networks                                                         | 445 |

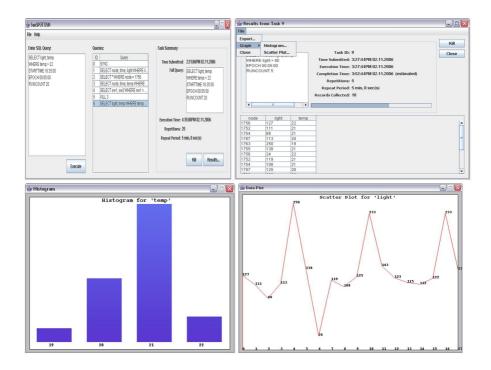

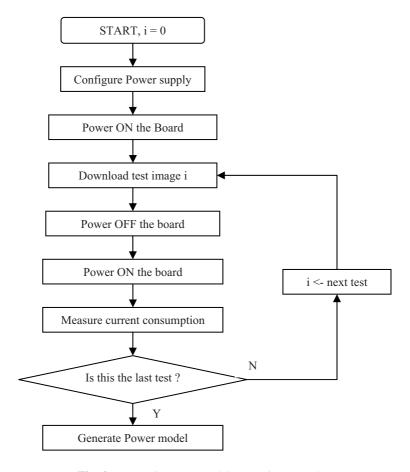

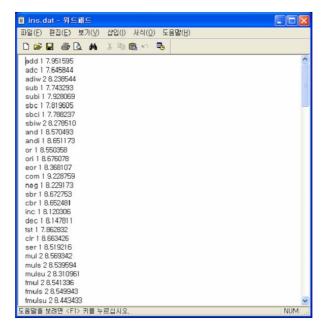

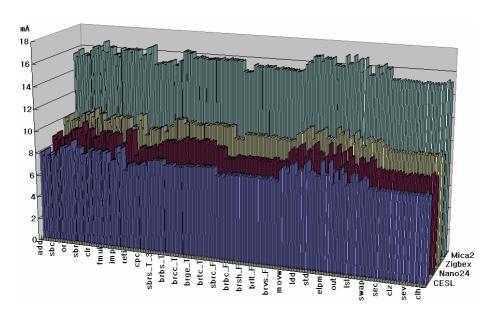

| Automatic Power Model Generation for Sensor Network Simulator Jaebok Park, Hyunwoo Joe, and Hyungshin Kim                      | 453 |

| Track 8: Real-Time Systems                                                                                                     |     |

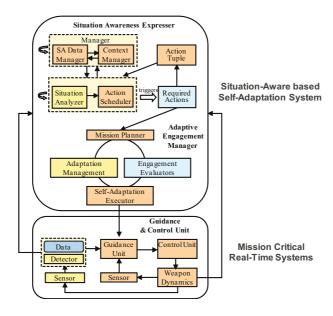

| Situation-Aware Based Self-adaptive Architecture for Mission Critical Systems                                                  | 464 |

| Table of Contents                                                                                                                                                               | XVII |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

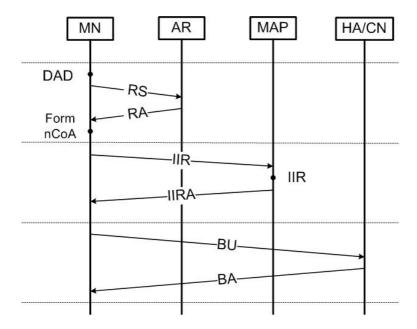

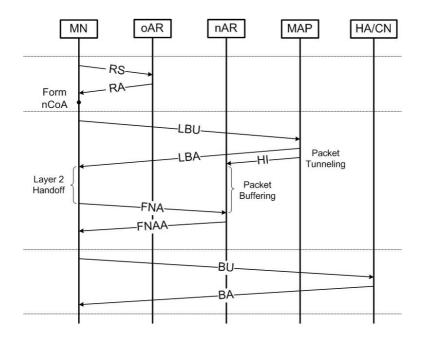

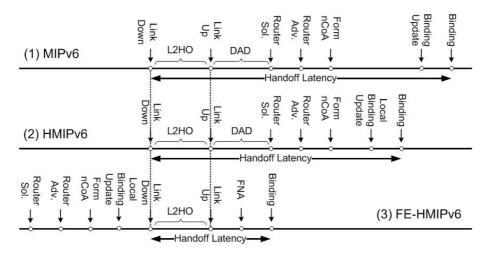

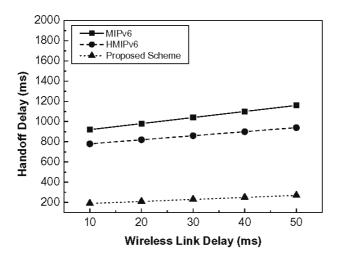

| Micromobility Management Enhancement for Fast Handover in HMIPv6-Based Real-Time Applications                                                                                   | 476  |

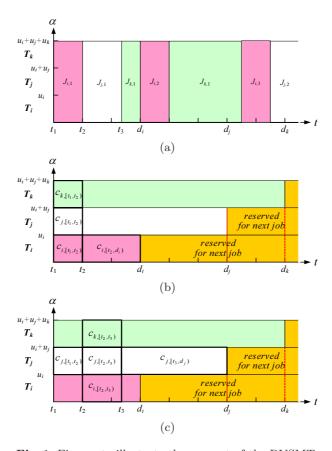

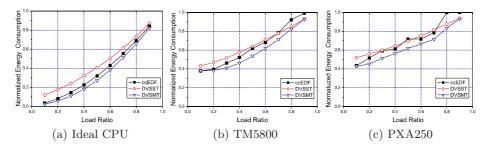

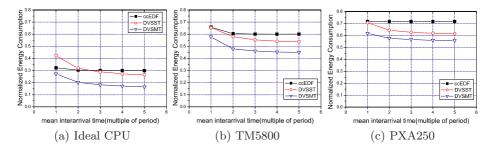

| DVSMT: Dynamic Voltage Scaling for Scheduling Mixed Real-Time Tasks                                                                                                             | 488  |

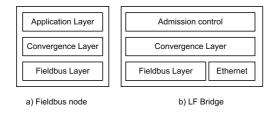

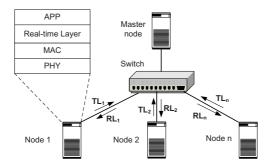

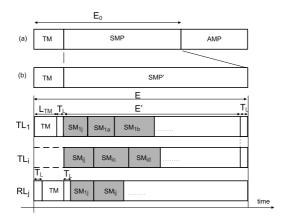

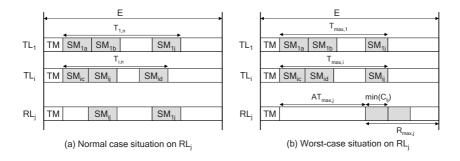

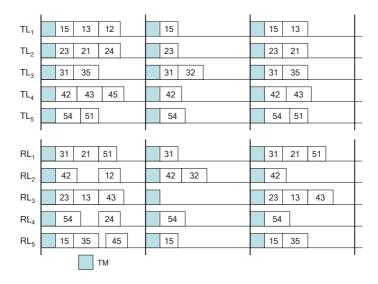

| Real-Time Communications on an Integrated Fieldbus Network Based on a Switched Ethernet in Industrial Environment                                                               | 498  |

| On Scheduling Exception Handlers in Dynamic, Embedded Real-Time Systems                                                                                                         | 510  |

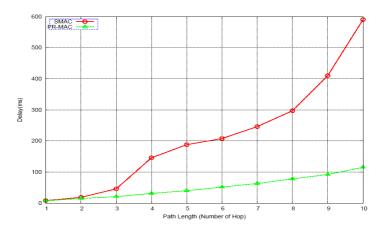

| PR-MAC: Path-Oriented Real-Time MAC Protocol for Wireless Sensor Network                                                                                                        | 530  |

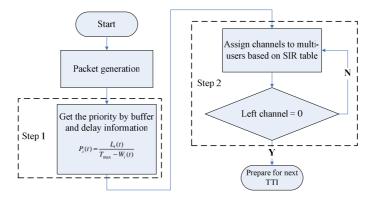

| Real-Time Traffic Packet Scheduling Algorithm in HSDPA System<br>Considering the Maximum Tolerable Delay and Channel Assignment<br>Xiaodong Yu, Sung Won Kim, and Yong Wan Park | 540  |

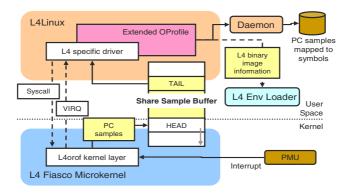

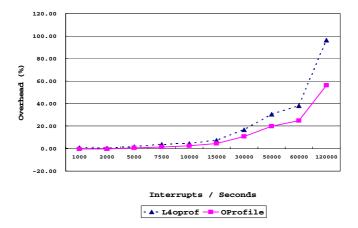

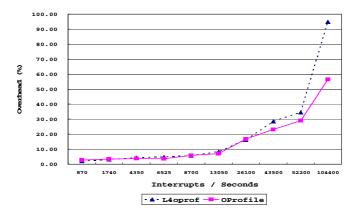

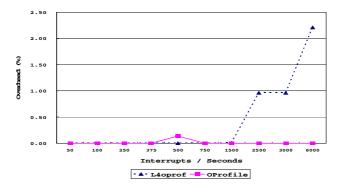

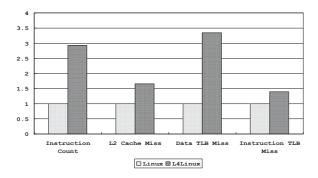

| L4oprof: A System-Wide Profiler Using Hardware PMU in L4 Environment                                                                                                            | 548  |

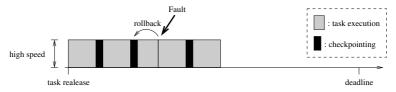

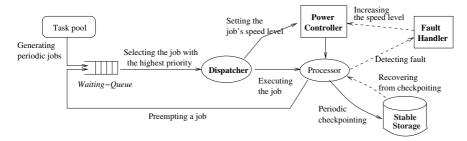

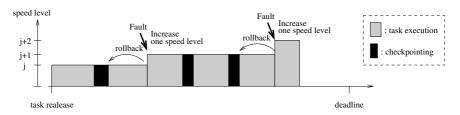

| An Adaptive DVS Checkpointing Scheme for Fixed-Priority Tasks with Reliability Constraints in Dependable Real-Time Embedded Systems Kyong Hoon Kim and Jong Kim                 | 560  |

| Energy-Efficient Fixed-Priority Scheduling for Periodic Real-Time Tasks with Multi-priority Subtasks                                                                            | 572  |

| A C-Language Binding for PSL                                                                                                                                                    | 584  |

| Track 9: Security and Dependability                                                                                                                                             |      |

| Cut Sequence Set Generation for Fault Tree Analysis                                                                                                                             | 592  |

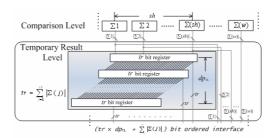

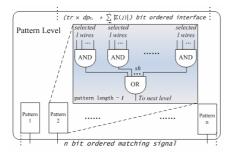

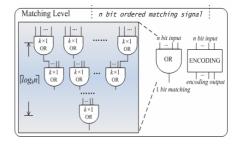

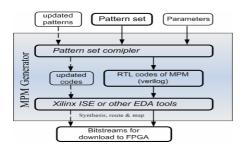

| Multilevel Pattern Matching Architecture for Network Intrusion Detection and Prevention System                                                                                  | 604  |

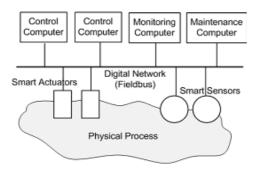

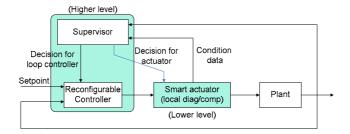

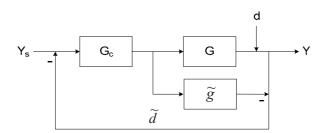

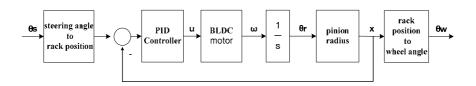

| Smart Actuator-Based Fault-Tolerant Control for Networked Safety-Critical Embedded Systems           | 615 |

|------------------------------------------------------------------------------------------------------|-----|

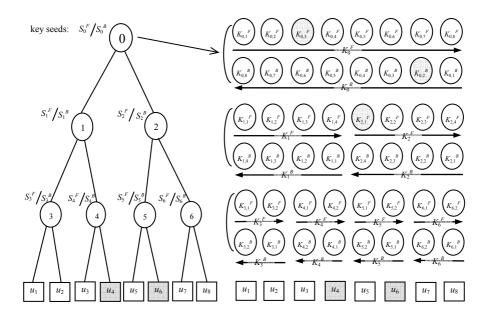

| KCT-Based Group Key Management Scheme in Clustered Wireless Sensor Networks                          | 627 |

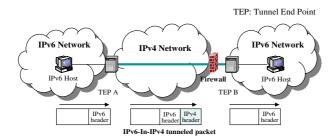

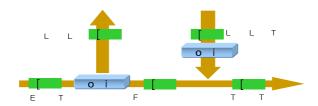

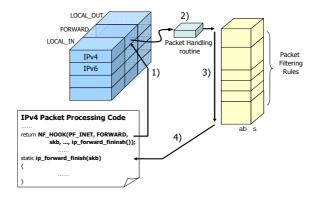

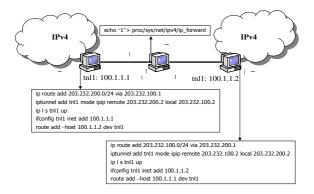

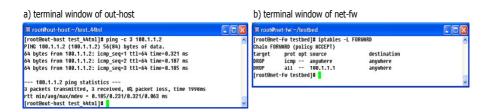

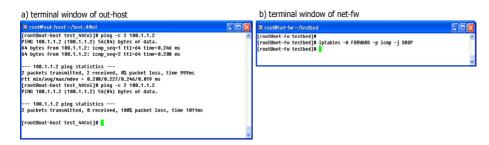

| A Secure Packet Filtering Mechanism for Tunneling over Internet                                      | 641 |

| Track 10: Wireless Communication                                                                     |     |

| An End-to-End Packet Delay Optimization for QoS in a MANET                                           | 653 |

| Power Efficient Relaying MAC Protocol for Rate Adaptive Wireless LANs                                | 664 |

| PHY-MAC Cross-Layer Design of Reliable Wireless Multicast Protocol with a Case Study of MB-OFDM WPAN | 676 |

| An Adaptive Multi-paths Algorithm for Wireless Sensor Networks  Zhendong Wu and Shanping Li          | 686 |

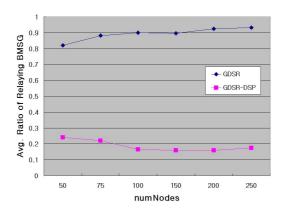

| Distributed Self-Pruning(DSP) Algorithm for Bridges in Clustered Ad<br>Hoc Networks                  | 699 |

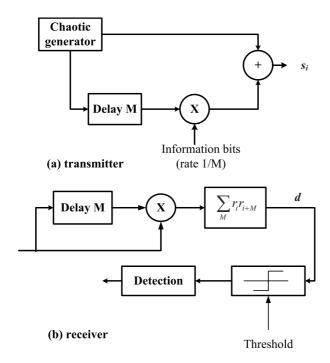

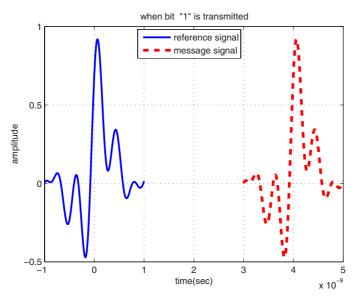

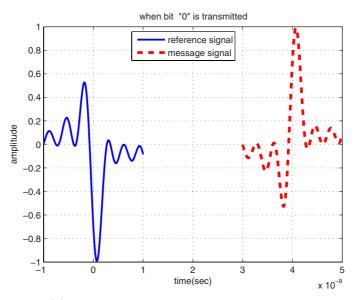

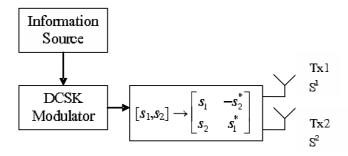

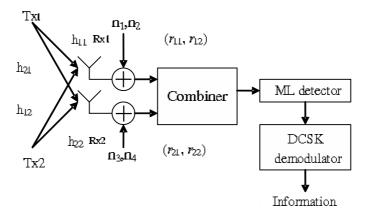

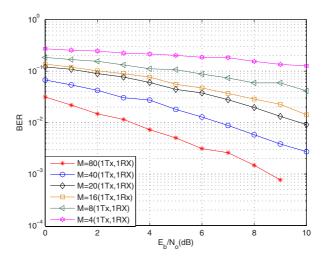

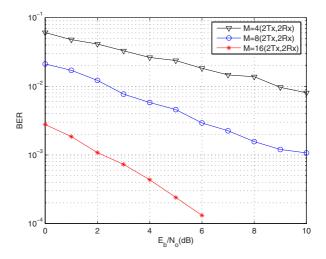

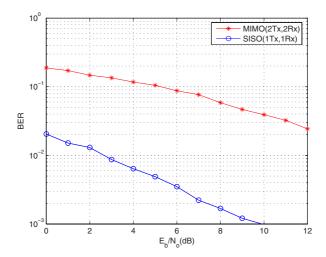

| Chaotic Communications in MIMO Systems                                                               | 708 |

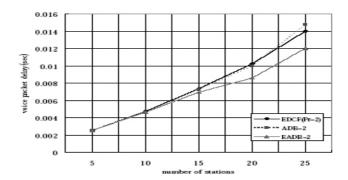

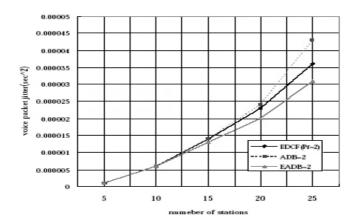

| A QoS Provisioning MAC Protocol for IEEE 802.11 WLANs                                                | 718 |

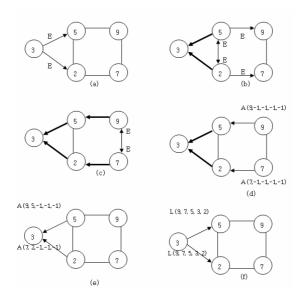

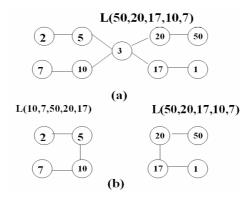

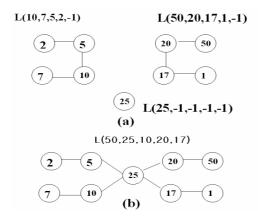

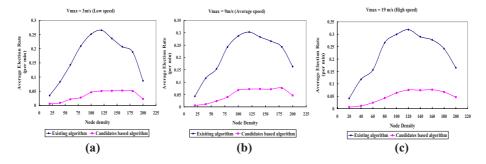

| A Leader Election Algorithm Within Candidates on Ad Hoc Mobile                                       | 700 |

| Networks                                                                                             | 728 |

| An Improvement of TCP Downstream Between Heterogeneous Terminals in an Infrastructure Network        | 739 |

# Object-Orientation Is Evil to Mobile Game: Experience from Industrial Mobile RPGs

Weishan Zhang<sup>1</sup>, Dong Han<sup>2</sup>, and Thomas Kunz<sup>3</sup>

<sup>1</sup> School of Software Engineering, Tongji University

No. 1239 Siping Road, Shanghai, 200092, China

zhangws@mail.tongji.edu.cn

<sup>2</sup> Department of Computer Science

Anhui Vocational College of Electronics &Information Technology

Bengbu University Park, Anhui Province, 233030, China

handongavceit@gmail.com

<sup>3</sup> Department of Systems and Computer Engineering, Carleton University

1125 Colonel By Drive, Ottawa, Canada K1S 5B6

tkunz@sce.carleton.ca

Abstract. Mobile gaming is playing an important role in the entertainment industry. Good performance is a critical requirement for mobile games in order to achieve acceptable running speed although mobile devices are limited by scarce resources. Object-oriented programming is the prevalent programming paradigm and this is true for mobile game development as well. As the origin of object-orientation (OO) is not targeting the embedded software domain, there is suspicion as to OO's usability for embedded software, especially with respect to mobile games. Questions arise like how OO and to what degree OO will affect the performance, executable file size, and how optimization strategies can improve the qualities of mobile game software. In this paper we investigate these questions within the mobile Role-Playing-Game (RPG) domain using five industrial mobile games developed with OO. We re-implemented these five RPGs with a structural programming style, by reducing the inheritance relationships, removing excessive classes and interfaces. Some additional optimizations are also applied during the re-implementation, such as the tackling of performance bottleneck methods, using more efficient algorithms. New games after optimizations run on average almost 25% faster than the corresponding original games, with a maximum of 34.62% improvement; the memory usage is decreased by more than 10% on average and 17.56% as a maximum; we also achieved a 59% code reduction and a 71% Jar file decrease after optimization. Therefore if developers are aiming for mobile game performance, we conclude that they should use as few OO features as possible. Structural programming can be a very competitive alternative.

#### 1 Introduction

Mobile games are one of the primary entertainment applications at present. Good performance is one of the top requirements for mobile games in spite of scarce resources on the mobile devices, such as low battery life, small memory and screen size, etc [1]. By performance we mean not only arithmetic operation time, but also memory

consumption of the game, how long it will take for the game to start, and finally the size of the executable program.

Currently Object-Oriented Programming (OOP) is the mainstream programming paradigm, and this is true for mobile game development as well. OOP is using abstractions where a collection of objects interact with each other, which is beneficial for achieving encapsulation and polymorphism. But every object will incur resource consumption which may lead to poor performance for embedded software [2], although this may not be a problem for desktop applications. And also there are shortcomings to the inheritance-based reuse, for example code redundancy and extra complexity [3].

Now it naturally comes to the questions of how OO affects the performance of the mobile games and to what degree, and how to optimize the performance. How and to what extent should we use the current OO languages for mobile game development? At present there is scarce published work to answer these questions with comprehensive case studies and convincing figures, especially in the mobile game domain. This kind of research is vital in order to help make decisions on what strategies should be used to improve the performance during the development of mobile games.

In this paper, we address these issues within the mobile RPG domain using five industrial mobile games developed with OO. We re-implemented these five RPGs using a more structural programming style, by reducing the inheritance relationships, removing excessive classes and interfaces and the tackling of performance bottleneck methods, using more efficient algorithms. With all these optimization strategies the performance of new games are improved significantly and the size of the final Jar file is reduced greatly. We conclude that application developers should use object orientation sparsely for mobile game development if performance is vital, and if one uses the OO language in a Structural Programming way, it could help boost the performance!

The rest of the paper is structured as follows: In the next section, we will briefly introduce the five RPGs and explain their implementation; then optimization strategies and techniques are discussed in Section 3. Section 4 illustrates the usage of these optimizations by re-implementing and re-structuring these five RPGs, mainly focusing on the shift to using structural programming. In Section 5, we evaluate the performance including the memory usage, loading time, Jar file size and Line of Code (LOC) metric. This is followed by a section to evaluate the design of these games using OO metrics. The concluding remarks and future work end the paper.

#### 2 Introduction to the Five Mobile RPGs

#### 2.1 Basic Information of the Five Mobile RPGs

The five mobile games named Dig (a), Climb (b), Hunt (c), Feeding (d) and Kongfu (e) are shown in Fig. 1 respectively. In Dig Gem, a hero digs around the map to look for gems. Different scores for different gems are added to the total and displayed in the upper left corner of the screen as shown in Fig. 1 (a). In Climb (Fig. 1 (b)) the hero walks and jumps on the floor to avoid falling down to the mountain. In Hunt (Fig. 1 (c)), the hero shoots animals and monsters with arrows and different scores will be added to the total for shooting different targets. In Feeding (Fig. 1 (d)), the

hero tries to pick up as much food as possible, with different scores for eating different types of food. In Kongfu (Fig. 1 (e)) we have two heroes and a 'learner' learns Kongfu skills from his 'master'.

Fig. 1. Five mobile RPGs

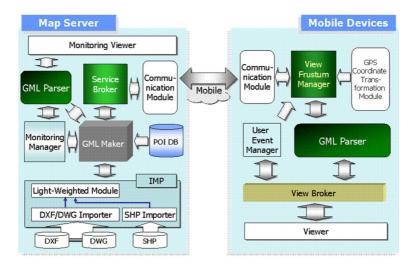

#### 2.2 Design and Implementation of the Mobile RPGs

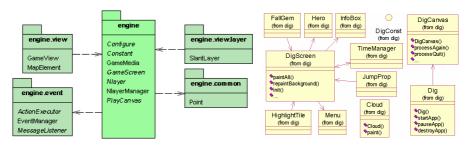

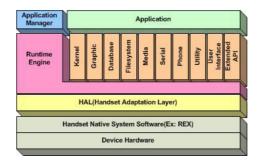

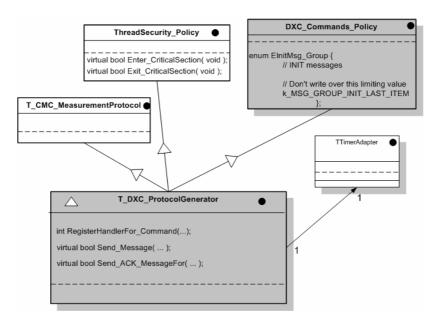

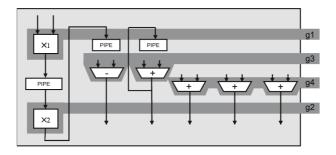

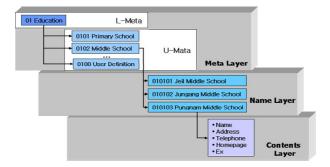

In order to improve the productivity of game development, a game engine is designed (Fig. 2) and used with all the five games. The game engine has components to abstract all common issues of game development. Package 'engine.view' is used for game view management. In 'engine' package there is a PlayCanvas class inheriting Game-Canvas from the J2ME [4] system library, layer management class Nlayer and NlayerManager, GameScreen etc. Package 'engine.viewlayer' realized the basic map operations where a three dimensional array is used to manage the map. Package 'engine.event' is used for event and message handling. All games and the game engine are developed with MIDP2.0 [4] where a new 'game' package is added to the system library after MIDP1.0 in order to facilitate game development with necessary APIs.

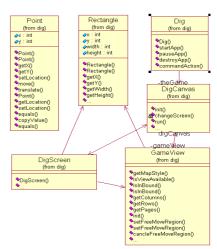

Because all games are based on the MIDP profile, the execution scenario and its control flow are similar: There is a main class that extends MIDlet (for example Dig class in Fig. 3), as required by MIDP. In the constructor of the main class, an instance of the game Canvas (for example DigCanvas) is created. Using a getInitialScreen() method, this instance creates a game starting screen object (for example DigScreen). In the starting screen, all initialization data are loaded, including map, sound, etc. The constructor of the game Canvas (for example DigCanvas) will call its super class constructor (PlayCanvas in 'engine' package), where the game thread is created and started. The thread then loops to monitor the input of the keyboard, to update the game screen in order to handle game logic, and to paint the canvas for the game.

Fig. 2. Package diagram for game engine

Fig. 3. Class diagram of Dig Gem

# 3 Performance Optimization Strategies and Techniques

#### 3.1 Evaluation of the Game Engine and Original RPGs

In this section we will first evaluate the design qualities of the game engine and all RPGs and then decide how to optimize them, using typical OO metrics [5]. These metrics are shown in later sections to facilitate the metrics comparisons between original games and the final optimized games. We used Together Architect 2006 [6] to collect the actual figures and used its default threshold for these metrics.

| OO Basic Metrics           | OO Coupling Metrics            | Inheritance based coupling |  |  |  |  |

|----------------------------|--------------------------------|----------------------------|--|--|--|--|

| CIW-Class Interface Width  | AOFD-Access Of Foreign Data    | DOIH-Depth Of Inheri-      |  |  |  |  |

| NAM-Number Of Accessor     | CBO-Coupling Between Objects   | tance Hierarchy            |  |  |  |  |

| Methods                    | CM-Changing Methods            | NOCC-Number Of Child       |  |  |  |  |

| NOA-Number Of Attributes   | DAC-Data Abstraction Coupling  | Classes                    |  |  |  |  |

| NOC-Number Of Classes      | DD-Dependency Dispersion       | TRAp-Total Reuse of        |  |  |  |  |

| NOCON-Number Of Con-       | FO-FanOut                      | Ancestor percentage        |  |  |  |  |

| structors                  | MIC-Method Invocation Coupling | TRAu-Total Reuse of        |  |  |  |  |

| NOIS-Number Of Import      | NCC-Number Of Client Classes   | Ancestor unitary           |  |  |  |  |

| Statements                 | NOCP-Number Of Client Packages | TRDp-Total Reuse in        |  |  |  |  |

| NOM-Number Of Members      | NOED-Number Of External Depen- | Descendants percentage     |  |  |  |  |

| NOO-Number Of Operations   | dicies                         | TRDu-Total Reuse in        |  |  |  |  |

| PIS-Package Interface Size | PUR-Package Usage Ratio        | Descendants unitary        |  |  |  |  |

| PS-Package Size            | VOD-Violations Of Demeters Law | _                          |  |  |  |  |

**Table 1.** OO metrics used for design quality evaluation

We also measured the polymorphism with Number Of Added Methods (NOAM), Number Of Overridden Methods (NOOM) and Polymorphism Factor (PF). All of them are fine except that 'engine.view.layer.Slantlayer' has NOOM of 5, which is still ok but we do think that there is potential to improve this as subclasses should generally extend the functionality of the parent classes rather than overriding them. And after the optimizations all NOOM are 1 if there is NOOM. Because the polymorphism measurements are not significant, we are not showing them in the paper.

The OO metrics measurement shows that the original five games are designed as normal OO programs, with inheritance-based reuse as main design objective. This provides us with a good opportunity to simplify the class relationships and re-implementing these games to check how the usage of object-oriented language in a structural programming way affects the performance, and to what degree.

#### 3.2 Optimization Strategies and Techniques

#### Methodological optimization

An object is the basic abstraction building block of OO, but more objects and classes will result in higher resource consumption. We try to solve this problem by minimizing the possible generated objects, simplifying class relationships. That is to say, we design our mobile game based on the traditional structural programing style and we check how this benefits the performance.

Some optimizations resulting from this choice are:

- a. Remove the constant interface. There are some constant interfaces, one for every game. But interfaces should be used solely for type definitions [7], therefore we should remove all constant interfaces for all the five games.

- b. Remove redundant inheritance relationships. In some cases, some classes that had very little in common were related by inheritance. We removed this kind of inheritance relationship along with unnecessary class members and methods.

- c. **Remove unnecessary classes.** We re-allocated functionalities so that some classes, especially those with very few methods, could be removed.

- d. **Remove obsolete class methods.** In some cases, we found that we never used certain class methods. We removed such obsolete methods.

- e. Find the performance bottleneck. For example, use WTK to inspect which method is the one that consumes most of the CPU and memory and then optimize it.

#### **Code optimization**

The objective is to minimize memory consumption and prevent memory leaks. Code optimization may include:

- f. Do not initialize all objects in the constructor and initialize it when first used.

- g. Change class members to local variables.

- h. Declare methods and variables final/static for faster access.

- i. Set an object to null if it isn't used any more which accelerates memory recycle.

#### Algorithm optimization

- j. Iterate loops down to zero as comparing against zero is faster.

- k. Move the arithmetic operation in a loop outside the loop body.

- l. Use bitwise operators (left shift/right shift) instead of multiplication and division.

#### **Exception handling**

- *m.* Return a null object instead of throwing exceptions wherever possible, or use if/then/else to handle different situation.

- n. Reuse an existing exception object rather than generating a new exception object.

#### **Datatype optimization**

Datatype optimization is an efficient way for improving performance as different data types use different resources.

- o. Replace resizable Vectors with arrays, if possible.

- p. Use primitive data type instead of the object type whenever possible.

- q. Minimize the usage of string concatenation and comparison, use StringBuffer instead.

# 4 Re-implement the Five Mobile RPGs Using Optimizations

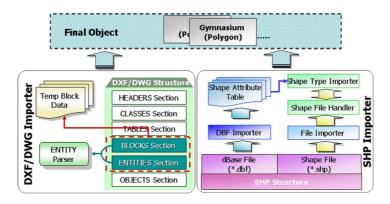

#### 4.1 Optimization on Inheritance, Class and Interface

Our main optimization approach is the shifting from the object-orientation style of implementation to the structural programming style, where we simplify the class relationships by reducing inheritance hierarchies, cut the number of classes and interfaces, and add new responsities to classes where his parent has been removed.

#### Remove the constant interface

For Dig gem, there is a DigConst interface. And the game engine package has two constant interfaces, Configure and Constant. All of them are removed and all the constants are defined in class DigScreen. The other four games are handled in the same way.

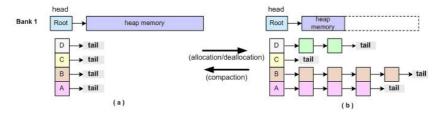

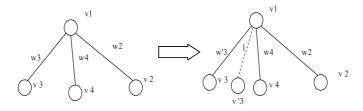

#### Remove unnecessary/redundant inheritance

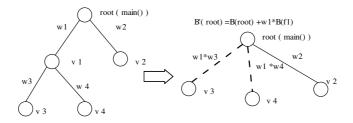

We know PlayCancas inherits GameCanvas and DigCanvas inherits PlayCanvas. And also from Fig. 8 we know that the DOIH of the original game and engine is 5 which exceeds the default upper threshold. Therefore our first optimization is to reduce the DOIH by simplifying the inheritance relationship. The three layer relationship can be simplified with DigCancas inheriting from GameCanvas directly. Therefore PlayCanvas is removed and DigCanvas is extended to take care of the responsibilities of PlayCanvas. Other usage of PlayCanvas will also be replaced with DigCanvas.

For the same reason and in the say way the GameScreen class in the engine package can also be removed and DigScreen can assume its responsibilities.

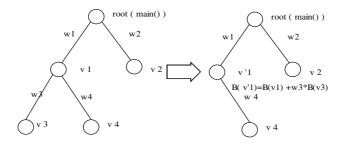

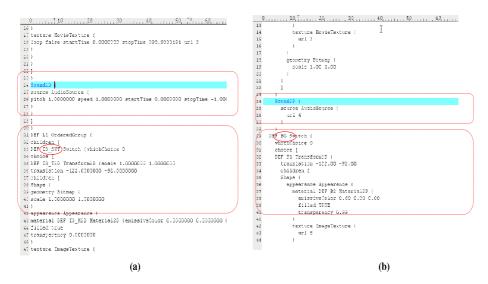

As we intended to remove all packages of the game engine, the inheritance between the 'dig.Hero' class and the 'engine.role.GameRole' class can be removed and replaced with the following new GameRole class (Fig. 4) by inheriting directly from J2ME system game library class Sprite.

```

public class GameRole extends Sprite {

public GameRole(){

super(DigScreen.loadImage

("dig/man.png"),32,30);

setRoleName("Hero");

this.setScrollView(true);

...// set action interval, speed }

public void doAction(int keyStates)

{

......}

```

Fig. 4. Redefined GameRole class

Fig. 5. Class diagram for Redesigned Dig gem

#### Remove unnecessary/redundant class and interface

- The 'engine.media.GameMedia' only defines some methods, and can be removed. The image related methods are now in the DigScreen class.

- Interface 'engine.view.layer.GroundMap' is only used by 'engine. view. layer.SlantLayer' and can be removed. All the contained methods are moved to SlantLayer.

- 'engine.view.GameScene' and 'engine.view.GameRole' form a GameView and therefore GameScene can be removed, all attributes and methods are now defined in GameView.

- Class 'engine.role.Motion' can be removed, and all attributes and methods are now defined in GameRole.

#### Remove obsolete class methods

For example in the GameMedia class, there are two methods for loading data from file or input stream, remaining from previous implementation, but never used in the current implementation. We remove such obsolete methods.

Other unnecessary classes include Menu, Color, Action, Event, EventManager, HotSpot, Message, Trigger, SoundCenter, MapElement; and unnecessary interfaces ActionExecutor, MessageListenable, MessageListener. All of them are removed. The class diagram for the redesigned Dig gem is shown in Fig. 5.

#### 4.2 Further Optimizations

#### Spotting the performance bottleneck

Method Profiler provided by WTK2.2 can be used to find which method(s) dominate the running time. We found that method paintGround() in 'dig.SlantLayer' takes 80.75% of Dig gem running time. Therefore optimization to this method would bring the biggest benefits. In the same way, other runtime-intensive methods of the other four games could be handled. For example, paintAll() in 'hunt.HuntScreen' which takes 81.03% of the running time of Hunt and should be optimized.

Take paintGround(Graphics g) as an example. We use the following techniques for optimization:

- declaring the method to be 'final';

- multiplication and division are replaced with bitwise operators;

- control variable in 'for' loop is compared with 0;

- arithmetic operations in loop body are moved out;

After these optimizations, the paintGround(Graphics g) method takes 71.38% of the running time, a decrease of 9.37%.

#### Change class members to local variables

For example, the following buffer size is defined in class GameMedia: public final static int BUFFER\_SIZE = 1024;

But BUFFER\_SIZE is used only in method LoadData() and it should be defined as a LoadData() local variable.

#### Declare method and variable as final/static for faster access

For example, in the DigScreen class the following code is used to make the access of the variable faster: public final static int MOTION\_FACE\_DOWN = 1; //  $\downarrow$

#### Using obfuscator

We use ProGuard2.7 [8] to obfuscate the five games. After obfuscation the Jar file decreases from 357KB to 326KB.

Other optimizations include setting objects to null if they are not used anymore, using a string buffer, etc.

# 5 Evaluation with Typical OO Metrics

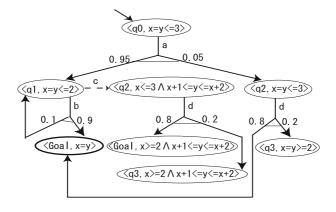

In this section, we will evalue the design of the original games and also the new games after optimization with typical OO metrics. We will first compare the results with packages, and then show the situation with Dig gem.

#### **Evaluation with OO basic metrics**

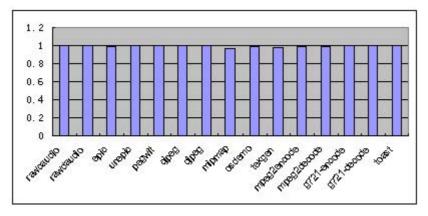

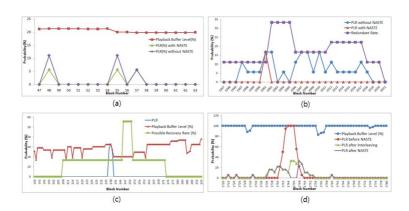

The Midlet suite name before optimization is MMMMM, and named MyGame\_Final after optimization. From Fig. 6, we could see that in myGame\_Final, NOM, NOO, NOA and NOCON are larger than the corresponding values in MMMMM. NOC, PS in MyGame\_Final are less than the corresponding values in MMMMM. This is because we have simplified the class relationships, which leads to an increase in the number of attributes and therefore results in bigger classes.

| Resource        | NOA | ١.  | N  | OC  | NO | CON | NOIS       | N    | OM  | NOO      | PIS      | PS |

|-----------------|-----|-----|----|-----|----|-----|------------|------|-----|----------|----------|----|

| — MMMMM         |     | 37  | 41 | 7   | 2  |     | 23         | 5    | 3   | 23       |          |    |

| + feeding       | 19  |     | 7  |     | 1  |     | 11         | 3    | 2   | 13       | 0        | 7  |

| + dig           |     | 37  | 12 | 2   | 1  |     | 17         | 5    | 3   | 16       | 3        | 12 |

| + hunt          | 29  |     | 11 | 1   | 1  |     | 23         | 5    | 2   | 23       | 0        | 11 |

| + climb         | 22  |     | 9  |     | 2  |     | 13         | 3    | 8   | 16       | 0        | 9  |

| + kongfu        | 23  |     | 8  |     | 2  |     | 12         | 3    | 3   | 13       | 0        | 8  |

| MyGame_Final    | 9   | 41  | 22 | 2   | 3  |     | 11         | 6    | 9   | 35       |          |    |

| + kongfu        | 29  |     | 4  |     | 3  |     | 7          | 4    | 8   | 25       | 0        | 4  |

| + climb         | 28  |     | 3  |     | 2  |     | 6          | 5    | 5   | 27       | 0        | 3  |

| ∓ dig           | •   | 41  | 6  |     | 3  |     | 9          | 6    | 9   | 31       | 0        | 6  |

| + hunt          |     | 33  | 5  |     | 3  |     | 11         | 6    | 5   | 35       | 0        | 5  |

| + feeding       | 25  |     | 4  |     | 3  |     | 5          | 4    | 7   | 25       | 0        | 4  |

| (a) OO basi     |     | CIW |    | NAM |    | NOA |            | NOIS | S 1 | TOM      | NOO      | P  |

| — MMMMM         |     |     |    |     |    | • 3 | 37         | 17   | 5   | 53       | 16       |    |

| di g            |     |     |    |     |    | • 3 | 37         | 17   | 5   | 3        | 16       | 13 |

| + DigScreen     |     | 12  |    | 2   |    | • 3 | 37         | 17   | 5   | 3        | 16       |    |

| + HighlightTile |     | 1   |    | 0   |    | 5   |            | 5    | 6   | 5        | 1        |    |

| + Hero          |     | 2   |    | 0   |    | 0   |            | 6    | 6   | Į        | 4        |    |

| + DigCanvas     |     | 6   |    | 0   |    | 4   |            | 10   | 1   | 13       | 9        |    |

| DigConst        |     | 40  |    | 0   |    | 0   |            | 0    | 0   | )        | 0        |    |

| + InfoBox       |     | 7   |    | 1   |    | 13  |            | 10   | 2   | 21       | 8        |    |

| + Menu          |     | 5   |    | 3   |    | 8   |            | 7    | 1   | 13       | 5        |    |

| + JumpProp      |     | 2   |    | 0   |    | 11  |            | 7    |     | 13       | 2        |    |

| + Dig           |     | 3   |    | 0   |    | 2   |            | 2    | 5   |          | 3        |    |

| + FallGem       |     | 1   |    | 0   |    | 6   |            | 6    | 7   |          | 1        |    |

| +Cloud          |     | 1   |    | 0   |    | 7   |            | 6    | 8   |          | 1        |    |

| + TimeManager   |     | 8   |    | 3   |    | 13  |            | 9    |     | 21       | 8        |    |

| - MyGame_Final  |     |     |    |     |    |     | 11         | 9    |     | 39       | 31       |    |

| di g            |     |     |    |     |    |     | 11         | 9    |     | 39       | 31       | 6  |

| + DigCanvas     |     | 18  |    | 2   |    | 17  |            | 4    |     | 38       | 21       |    |

| + Dig           |     | 4   |    | 0   |    | 5   |            | 5    |     | 9        | 4        |    |

| + Rectangle     |     | 25  |    | 4   |    | 4   |            | 0    |     | 25       | 21       |    |

|                 |     | 12  |    | 2   |    | 2   |            | 0    |     | 12       | 10       |    |

| + Point         |     |     |    |     |    |     |            |      |     |          |          |    |

|                 |     | 20  |    | 7   |    | 8   | <b>1</b> 1 | 6    |     | 28<br>59 | 20<br>31 |    |

1 86

Fig. 6. OO basic metrics comparison

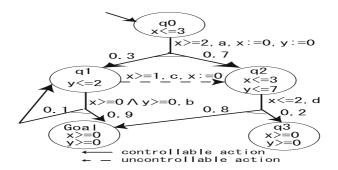

#### **OO Coupling Metrics**

Fig. 7 shows OO coupling metrics of the game packages and also Dig gem. We can see that before optimization, package 'dig' and 'hunt' have high degree of coupling. The DAC value of package 'climb', 'kongfu' and 'feeding' exceed the default threshold. Although not shown here, the values of DAC and FO of package 'engine.view'

also exceed the upper default limit. This means that the original design of the 'engine' package was focusing on reuse but was not caring much about coupling.

After optimization we actually lower some of the coupling metrics, and leave the others at the same level. Big differences happened to package 'dig' before and after optimization, where we lower all metrics except the FO, which is not a problem as Digscreen deliberately is assigned more responsibilities during our re-implementation.

| Resource                                    | CB0   | DA           | C  | FC     | )         | MIC | NC | C            | NOCP       | PUR | 70  | D           |

|---------------------------------------------|-------|--------------|----|--------|-----------|-----|----|--------------|------------|-----|-----|-------------|

| - MMMMM                                     | • 35  | •            | 14 |        | 20        | 50  |    |              |            |     | 12  |             |

| + climb                                     | 20    |              | 9  | 12     | 2         | 24  | 0  |              | 0          | 0   | 5   |             |

| + dig                                       | • 33  |              | 12 |        | 16        | 50  | 1  |              | 1          | 25  | 12  |             |

| + feeding                                   | 17    |              | 7  | 10     | )         | 22  | 0  |              | 0          | 0   | 4   |             |

| + hunt                                      | • 35  |              | 14 |        | 20        | 48  | 0  |              | 0          | 0   | 11  |             |

| + kongfu                                    | 17    | •            | 7  | 10     | )         | 20  | 0  |              | 0          | 0   | 4   |             |

| - MyGame_Final                              | 22    | •            | 12 |        | 22        | 14  |    |              |            |     | 7   |             |

| + climb                                     | 15    | •            | 10 | 13     | 3         | 10  | 0  |              | 0          | 0   | 5   |             |

| + dig                                       | 21    | •            | 11 |        | 19        | 14  | 0  |              | 0          | 0   | 7   |             |

| + feeding                                   | 12    | •            | 8  | 12     | 2         | 14  | 0  |              | 0          | 0   | 4   |             |

| + hunt                                      | 22    |              | 12 |        | 22        | 14  | 0  |              | 0          | 0   | 7   |             |

| + kongfu                                    | 12    |              | 8  | 12     | 2         | 14  | 0  |              | 0          | 0   | 4   |             |

| MMMM                                        | AOFD  | • 33         | -  | CM     | • 12      | DD  |    | FO 16        | MIC<br>209 | NO  | ED  | 1           |

|                                             | NOT D |              | _  | OIII   | _         | _   | _  |              | _          | 110 | LD. | _           |

| dig                                         |       | • 33         |    |        | • 12      |     |    |              | 209        |     |     | 1           |

| +Cloud                                      | 1     | 5            |    | 1      | 3         | 3   |    | 4            | 9          | 6   |     | 1           |

| + Dig                                       | Ô     | 4            |    | 1      | 2         | 3   |    | 2            | 9          | 4   |     | 1           |

| + DigCanvas                                 | 2     | 12           |    | 0      | 4         | 6   |    | 6            | 82         | 13  |     | 4           |

| DigConst                                    | 0     | 0            |    | 14     | ò         | 1   |    | 0            | 0          | 0   |     | 0           |

| + DigScreen                                 | 7     | • 33         |    | 3      | • 12      |     |    |              | 209        | 26  |     | 1           |

| + FallGem                                   | 2     | 8            |    | 1      | 3         | 3   |    | 4            | 18         | 6   |     | 2           |

| + Hero                                      | 3     | 6            |    | 2      | 0         | 4   |    | 0            | 36         | 6   |     | 1           |

| + HighlightTile                             | 2     | 7            |    | 2      | 2         | 3   |    | 4            | 18         | 6   |     | 2           |

| + InfoBox                                   | 3     | 9            |    | 3      | 3         | 5   |    | 4            | 27         | 10  |     | 2           |

| + JumpProp                                  | 2     | 7            |    | 1      | 3         | 3   |    | 4            | 27         | 7   |     | 1           |

| + Menu                                      | 2     | 7            |    | 1      | 3         | 4   |    | 4            | 9          | 8   |     | 2           |

|                                             | 2     | 6            |    | 4      | 3         | 3   |    | 4            | 18         | 5   |     | 1           |

| + TimeManager                               | ~     |              |    |        | • 11      |     |    | 19           | 60         |     |     | 1           |

| lyGame_Final                                | -     | 21           |    |        |           |     |    |              |            |     |     | 7           |

| lyGame_Final                                | _     | 21           |    |        | • 11      |     |    |              | 60         |     |     | 7           |

| yGame_Final<br>- dig<br>- Dig               | 1     | 21<br>5      |    | 1      | • 11<br>3 | 2   |    | 19<br>4      | 60<br>40   | 5   |     | 7           |

| lyGame_Final<br>dig<br>+ Dig<br>+ DigCanvas |       | 21<br>5<br>7 |    | 1<br>8 | • 11      | 2 4 |    | 19           | 60         | 3   |     | 7<br>7<br>1 |

| lyGame_Final<br>- dig<br>+ Dig              | 1     | 21<br>5      |    |        | • 11<br>3 |     |    | 19<br>4<br>6 | 60<br>40   |     |     | 7           |

(a) OO coupling metrics comparison for Dig gem

Fig. 7. OO coupling metrics comparisons

+ Point

| Resource              | DOIH | NOCC | TRAp | TRAu | TRDp | TRDu |

|-----------------------|------|------|------|------|------|------|

| - MMMMM               | • 5  | 28   | 27   | 100  | 287  | 859  |

| + engine. view        | 1    | 1    | 4    | 33   | 3    | 17   |

| + climb               | • 5  | 0    | 11   | 80   | 0    | 0    |

| + engine. event       | 0    | 11   | 0    | 0    | 3    | 100  |

| + guessdual           | • 5  | 0    | 20   | 90   | 0    | 0    |

| + sanjie              | 4    | 12   | 0    | 0    | 0    | 0    |

| + engine.common       | 0    | 0    | 0    | 0    | 0    | 0    |

| + engine              | 4    | 28   | 0    | 0    | 287  | 859  |

| + hunt                | • 5  | 0    | 27   | 100  | 0    | 0    |

| + kongfu              | • 5  | 0    | 8    | 80   | 0    | 0    |

| + dig                 | • 5  | 0    | 27   | 100  | 0    | 0    |

| + feeding             | • 5  | 0    | 9    | 80   | 0    | 0    |

| + engine. view. layer | 1    | 1    | 2    | 18   | 0    | 0    |

| + engine.role         | 3    | 4    | 0    | 0    | 29   | 138  |

| + engine. media       | 0    | 0    | 0    | 0    | 0    | 0    |

| MyGame_Final          | 2    | 0    | 0    | 0    | 0    | 0    |

| + feeding             | 2    | 0    | 0    | 0    | 0    | 0    |

| + kongfu              | 2    | 0    | 0    | 0    | 0    | 0    |

| + hunt                | 2    | 0    | 0    | 0    | 0    | 0    |

| + climb               | 2    | 0    | 0    | 0    | 0    | 0    |

| + dig                 | 2    | 0    | 0    | 0    | 0    | 0    |

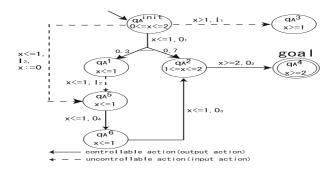

Fig. 8. Inheritance based coupling comparisons

#### **OO** Inheritance Metrics

Fig. 8 shows the OO inheritance-based coupling measurement. Before optimization, DOIH of games in MMMMM is 5, which is a bit high, exceeding the upper default bound, which motivates us to simplify the design and reduce the inheritance hierarchy. The DOIH becomes 2 after re-implementation. It is obvious that the original game design makes good use of inheritance-based reuse, while we are not using this at all as intended.

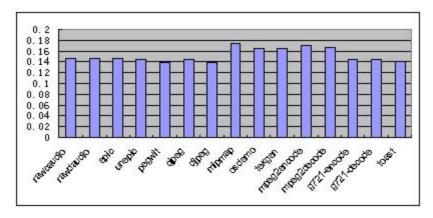

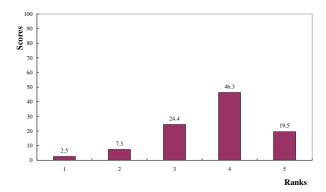

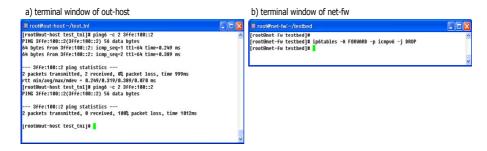

# 6 Experimental Results and Discussion

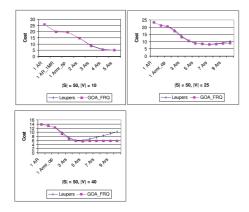

We compared the performance before and after optimizations shown in Table 2 and Table 3. The figures were obtained with Wireless Toolkit 2.2 (with memory monitor and profiler turned on in order to slow the running of these games to facilitate all measurements) on Windows 2000 Server service pack 3, 256M RAM, x86 Family 6 Model 8 Stepping 1 Authentic AMD 1499Mhz.

|         |        | 1      | 2      | 3      | Average | Improvements |

|---------|--------|--------|--------|--------|---------|--------------|

| D:      | Before | 263624 | 279436 | 264052 | 269037  | 17.56%       |

| Dig gem | After  | 220460 | 220764 | 224152 | 221792  | 17.30%       |

| Hunt    | Before | 139296 | 145278 | 143662 | 142745  | 16.30%       |

| riulit  | After  | 118800 | 120240 | 119398 | 119479  | 10.30 %      |

| Climb   | Before | 337612 | 333864 | 334523 | 335333  | 4.80%        |

|         | After  | 318975 | 321827 | 316958 | 319253  | 4.80 //      |

| Feeding | Before | 345232 | 354532 | 354396 | 351387  | 5.85%        |

|         | After  | 328791 | 336948 | 326743 | 330827  | 3.63 //      |

| Kongfu  | Before | 350420 | 350000 | 333992 | 344781  | 7.51%        |

| Kongru  | After  | 31068  | 327263 | 318689 | 318877  | 7.5170       |

**Table 2.** Maximum memory usage comparison

| Table 3. | Loading | time | comparisons |

|----------|---------|------|-------------|

|          |         |      |             |

|          |        | 1      | 2     | 3     | Average | Improvements |

|----------|--------|--------|-------|-------|---------|--------------|

| Dig gem  | Before | Before | 79.37 | 79.86 | 79.28   | 22.73%       |

| Dig geni | After  | After  | 61.10 | 61.84 | 61.36   | 22.1370      |

| Hunt     | Before | Before | 6.17  | 5.68  | 6.77    | 34.62%       |

| Trunt    | After  | After  | 4.15  | 3.64  | 4.39    | 34.02 //     |

| Climb    | Before | Before | 4.70  | 5.19  | 5.23    | 25.79%       |

| Cimio    | After  | After  | 3.89  | 3.22  | 4.10    | 23.1770      |

| Feeding  | Before | Before | 3.63  | 3.53  | 3.55    | 24.65%       |

| recuing  | After  | After  | 2.80  | 2.39  | 2.88    | 24.03 //     |

| Kongfu   | Before | Before | 5.29  | 5.19  | 5.32    | 16.70%       |

| Kongru   | After  | After  | 4.34  | 4.87  | 3.96    | 10.7070      |

From Table 2 we can see that the new games, after optimizations, have better memory usage, with a maximum of almost 18% less memory and minimum reduction of almost 5%. This decrease is due to the fact that we are using less classes and interfaces and save heap usage during execution. We also improved the loading time

(Table 3) significantly after optimization, and the loading time of each optimized game decreases 22.73%, 34.62%, 25.79%, 24.65% and 16.70% respectively.

We also checked the LOC differences before and after optimizations. The LOC has been reduced from 21597 LOC to 8868, a 59% decrease. The Jar file decreased from 1.12MB to 326KB, and we obtained a 71% reduction after optimization.

These performance improvements are due to applying optimization strategies across all the games, mainly motivated by the usage of a more structural programming style.

#### 7 Related Work

Mobile games are very popular and there are a number of online resources discussing the optimization of mobile games, e.g. [9]. They discuss various optimization techniques that could be used and also have been (or can be) incorporated in our work. Books like [7] also contain valuable suggestions for writing good Java programs that are not restricted to J2ME. But none of them provides us with convincing figures and a comprehensive case study to shown the actual impact of such optimizations.

There are company-specific guide-lines for the development of mobile games [10]. While they are very important and if possible, the usage of company-specific libraries usually is a wise option for improve the performance of the mobile games, we tried to be company-neutral in our research, which could be universal to all available devices.

Klingauf et al. [11] present a radical shift from the conventional approach to a native programming language like C to implement the whole system library and a high-level C-to-Java interface. This is very good in case this strategy is adopted by companies. We doubt though that this is a practical way for the companies who deliver mobile phones and mobile games. We present our optimizations and show how they affect the performance and all of them are very practical and useful.

There is an automatic J2ME games optimization tool called mBooster [12], designed mainly to minimize JAR file size. It can perform automatic class and interface merging and other low-level optimizations. But there are obvious limitations for its usage, for example it cannot perform class merging if the two candidate classes are in different packages. There is no mention on what criteria it uses to do class merging. But it does give us some ideas for implementing our own tool for optimizations.

#### 8 Conclusions and Future Work

Mobile gaming is playing a more and more important role in the entertainment industry. Although object-oriented programming is the prevalent programming paradigm and OO is used widely for mobile game development, it is very doubtful to use object orientation in the embedded software domain because of its intrinsic problems. There arise questions like how OO and to what degree OO will affect the performance, executable file size, and how optimization strategies can improve the qualities of mobile game software. In this paper we investigated these questions using five industrial mobile games developed with OO.

We re-implemented these five RPGs with the style of structural programming, by reducing the inheritance relationships, removing excessive classes and interfaces. And also some other optimizations are used during the re-implementation, such as the tackling of performance bottleneck methods, using more efficient algorithms. After optimization, the loading time is significantly improved, on average almost 25% faster than loading the corresponding original games, and a maximum of 34.62% improvement; the memory usage is decreased by more than 10% on average and 17.56% as a maximum; we also achieved a 59% code reduction and a 71% Jar file decrease after optimization.

Therefore we conclude that if developers are going for mobile game performance, they should use as few OO features as possible because of the footprint of objects. Structural programming can be a very competitive alternative. It may seem strange to advocate using object oriented language with a structural programming style, but we found that this is a promising way to improve performance.

We will continue our work in two directions, the first is to explore the reuse based mobile game development using Frame concepts and technologies where we have expertise [13], the second is to design and implement an automatic tool support for Frame based and optimized mobile game development which is inspired by mBooster.

# Acknowledgements

Thanks to Liu Wei and other authors from Meitong Co. Ltd. who have implemented the original games. We also owe our great thanks to Prof. Klaus Marius Hansen from University of Aarhus, and the generous support from the EU HYDRA project.

#### References

- Blow J. Game Development: Harder Than You Think. Game DevelopmentVol. 1, No. 10, February 2004

- Maarten Boasson. Embedded systems unsuitable for object orientation. 7th Ada-Europe International Conference on Reliable Software Technologies, Vienna, Austria, June 2002. pp.1-12

- Object Oriented Programming Oversold. http://www.geocities.com/tablizer/oopbad.htm. 2007-3-10

- 4. J2ME homepage. http://java.sun.com/javame/index.jsp. 2007-3-10

- Marinescu R. An Object Oriented Metrics Suite on Coupling. Master's thesis, Polytechnic University of Timisoara, 1998

- Borland together Architect homepage http://www.borland.com/ downloads/ download\_ together.html. 2007-3-10

- 7. Michael C. Daconta, et al. More java pitfalls. Wiley, 2003

- 8. Proguard homepage. http://proguard.sourceforge.net/. 2007-3-10

- 9. Supremej2me website. http://supremej2me.bambalam.se/. 2007-3-10

- Nokia. Designing MIDP applications for optimization. http://sw.nokia.com/id/ 89527700c7ff/. 2007-3-10

- W. Klingauf, L. Witte, U. Golze. Performance Optimization of Embedded Java Applications by a C/Java-hybrid Architecture. Global Signal Processing Conference, Santa Clara, CA, Sept. 2004

- 12. mBooster homepage. http://innaworks.com/mBooster.html. 2007-3-10

- W. Zhang, S. Jarzabek. Reuse without Compromising Performance: Industrial Experience from RPG Software Product Line for Mobile Devices. Proc. of SPLC2005. Rennes, Sept. 2005, LNCS3714, pp. 57-69

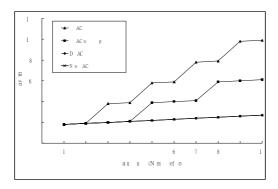

# Device-Aware Cache Replacement Algorithm for Heterogeneous Mobile Storage Devices

Young-Jin Kim and Jihong Kim

School of Computer Science & Engineering, Seoul National University, San 56-1 Shillim-dong, Kwanak-gu, Seoul, Korea, 151-742 {youngjk,jihong}@davinci.snu.ac.kr

Abstract. Hard disks, most prevalent mass-storage devices, have high power consumption and high response time for random I/O requests. Recent remarkable technology improvement of flash memory has made it a rising secondary storage device but flash memory still has high cost per bit. Usage of heterogeneous storage devices such as a pair of a hard disk and a flash memory can provide reasonable cost, relatively acceptable response time, and low-power consumption. In this paper, we propose a novel buffer cache replacement algorithm which targets a mobile computing system with a heterogeneous storage pair of a hard disk and a flash memory. The algorithm partitions the cache per each device and adjusts the size of each partition based on the performance indices of the devices, and manages each partition according to workload patterns. Simulations show that the proposed algorithm yields a hit rate up to two times higher than LRU on the typical mobile traces according to the cache size and achieves also better system I/O response time and energy consumption.

**Keywords:** Heterogeneous storage, mobile systems, device-aware, work-load-aware, cache replacement.

#### 1 Introduction

As the mobile and ubiquitous computing technology progresses, end-users tend to want that they can use high-performance and high I/O load applications such as games and MPEG players. In the last decade, the innovational development of processors, memories, network devices, and secondary storage devices has enabled this. These days mobile computing systems with high-capacity storage devices are popular, such as PDAs, PMPs, and MP3 players. Since hard disk drives are widely adopted for mobile computing platforms, the demand for hard disk drives with a small form-factor (2.5" or less), embedded in or connected to such systems, is also incrementally rising [1]. Concurrently, due to recent remarkable technology improvement of flash memory, it appears a rising secondary storage device.

However, despite attractive low cost per bit, hard disks are big power consumers and have poor performance for random I/O requests. Flash memory still

has relatively high cost per bit. For example, NAND flash memory is said to be at least several times more expensive than disk drives with the same capacities [2]. Therefore, complementary storage architectures or techniques have been emerging. Several researchers have proposed combined storage techniques with a flash memory and a hard disk, which can be categorized into two: 1) using a flash memory as a non-volatile cache [3,4,5,6,7,8,9]; 2) using a flash memory as a secondary storage device [10]. Specially, [10] studied the potential of heterogeneous secondary storage by employing these two devices together with data concentration techniques. The heterogeneous storage solution in this work is expected to yield more energy saving in that it employs a flash memory as a secondary storage device directly and can maintain a larger set of energy-hungry blocks altogether on it compared with other work. However, the authors did not investigate performance improvement or load balancing problems deeply.

In case of using heterogeneous devices generally, file systems require caching algorithms that take into account the different miss penalties across file blocks depending on which devices they belong to. But, the most commonly used cache replacement algorithm, LRU is not aware of such different cost and treats all cache blocks as if they have the same replacement costs. In the web cache communities, there have been abundant research results on cost-aware cache replacement algorithms, which consider different file size, network latency during re-fetch due to a cache miss, file access frequency, etc. Recent web cache algorithms may be based on or enhance the *GreedyDual-Size* algorithm [11], which incorporates locality with miss penalty and file size concerns, generalizing the LRU algorithm. In disk-based storage systems, [12] studied storage-aware cache management algorithms using different costs on heterogeneous disks. This work maintained one partition per each disk and adjusted partition sizes based on the time spent per each disk (they call this wait time) over a period of device requests, and controlled the blocks within each partition similarly to the GreedyDual-Size algorithm. But, the authors did not take into account minutely the case of there being a number of sequential accesses, which may be problematic in their algorithms. This is because if a considerable number of sequential accesses are requested to a disk its wait time can be lengthened and the corresponding partition size will increase filling this partition with less valuable blocks. Consequently, in the worst case this algorithm may fail in obtaining good load balance.

In this paper, we build a novel cache replacement algorithm to overcome such limit, which targets mobile storage systems exploiting a pair of a hard disk and a flash memory as secondary storage. Our algorithm intends to enhance the system performance through both device-aware and workload-aware load balancing. For the former we use cache miss counts and access time per device and for the latter we have our algorithm manage the cache in the direction of exploiting the fast sequential performance feature of a hard disk. To the best of our knowledge, our work is the first attempt to design and incorporate a cost-aware cache management algorithm on the heterogeneous combination of a hard disk and a flash memory.

Our first goal is to investigate how our device-aware cache replacement algorithm can balance the I/O load between two heterogeneous devices on typical mobile workloads when the target system employs a hard disk and a flash memory as mass storage, compared with LRU. Second goal is to study how well our cache algorithm avoids cache pollution incurred by sequential block requests while balancing the I/O load.

We first tackle the design of a workload-aware cache replacement algorithm (in short, WAC) by introducing different cost per workload pattern similarly to the GreedyDual-Size algorithm. Then, we propose our re-partitioning policy on the total cache based on the cache miss counts at a fixed period and finally complete to embody our device-aware cache replacement algorithm (in short, DAC) combining these.

The rest of this paper is organized as follows. In Section 2, we review the features of a hard disk and a NAND flash memory to compose heterogeneous storage on mobile platforms and describe requirements for designing a device-aware cache replacement algorithm briefly. In Section 3, we describe our both workload-aware and device-aware algorithms in detail. Section 4 presents our simulation framework and simulation results. Related work is given in Section 5. Finally, we conclude in Section 6.

#### 2 Motivation

#### 2.1 Device Bandwidth and Sequentiality

Since our research targets heterogeneous storage systems with the configuration of a hard disk and a flash memory, it is necessary to examine the features of a hard disk and a flash memory. For this purpose, we simply take two typical devices as shown in Table 1, which are appropriate for mobile storage. Fujitsu MHT060BH has a 2.5" form factor, a 60 GB capacity, and 5,400 RPM while Samsung K9K1208U is a NAND flash memory and has a 64 MB capacity, a block size of 16 KB, and a page size of 512 B. The throughputs of the flash memory were from [13] and those of the hard disk were obtained on our Sony VAIO laptop computer which embeds this disk using DiskSpd [14], which can measure disk I/O performance with various configurations including whether I/Os are sequential or random on Windows XP.

| Device            |            |       | Hard disk | Flash memory |

|-------------------|------------|-------|-----------|--------------|

|                   |            |       | MHT2060BH | K9K1208U     |

| Throughput (MB/s) | Sequential | Read  | 30.47     | 14.3         |

|                   |            | Write | 30.47     | 1.78         |

|                   | Random     | Read  | 6.6       | 14.3         |

|                   |            | Write | 6.6       | 1.78         |

Table 1. Throughputs of a laptop disk and a NAND flash memory

In Table 1, the disk shows a pretty good throughput for sequential I/Os and the value is about 5 times larger than that for random I/Os irrespective of the I/O type. In contrast to the disk, the flash memory doesn't concern sequentiality of I/Os and exhibits poor performance for write I/Os compared with reads. Therefore, when we design and use a heterogeneous storage system with such devices we surely need to meet performance imbalance which is likely to occur due to distinctly separable characteristics of these devices. This is because realistic workloads on mobile platforms often exhibit mixed patterns of sequential and random I/O operations like the case of concurrent execution of MP3 playing and program compiling. In addition, the conventional operating systems might not be designed well for I/O sequentiality coupled with this new and unfamiliar configuration of heterogeneous devices. For example, it seems that adequate management of sequentiality and I/O type for block requests across these heterogeneous devices in the viewpoint of performance may beyond the capability of the LRU algorithm as previously remarked.

#### 2.2 Mobile Workloads and Sequentiality

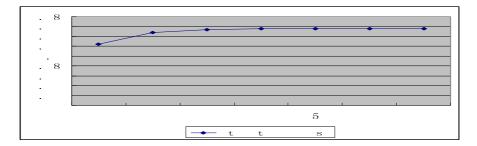

Recent studies on mobile storage systems collected and utilized traces on applications typically used in mobile computing environments under feasible execution scenarios [5,10]. Among these, [10] gathered traces while executing real applications which can be used for a PDA immediately on an evaluation board similar to a PDA. The used execution scenario was repetition of file transfer, email, file search, and sleep (no operation). We examined the behavior of this mobile workload (hereafter, we will call PDA trace).

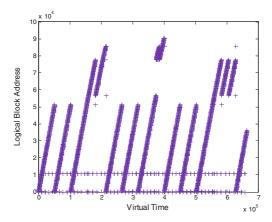

Since file transfer gives rise to disk reads (or writes) when files are sent to (or from) a network, the access pattern will be shown to be long sequential. The other applications except sleep are likely to exhibit random accesses (in this paper, a random access type means non-sequential one). Figure 1 shows the access pattern of the PDA trace, where x axis is virtual time (i.e., index of arriving requests) and y axis is logical block address. We notice that there are mixed accesses of a large number of sequential accesses, big and small loop-type accesses, and a small amount of temporal accesses. Similar access patterns can be found in the plots of traces gathered under programming and networking scenarios for mobile computing platforms in [5], though there is a different level of sequentiality compared with the PDA trace. Such observations drive us to need to deal with frequent sequential I/O operations together with random I/Os because if they weren't coped with adequately at the operating system software level there might occur critical performance degradation of the overall system.

# 3 Device-Aware Cache Replacement Algorithm

# 3.1 Workload-Aware Cache Algorithm

As was described in the previous section, it is requisite to deal with mixed access patterns which may frequently occur on generic mobile computing platforms

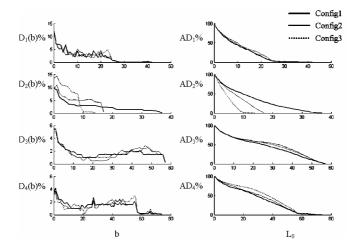

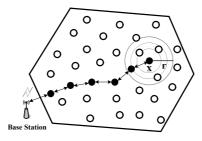

Fig. 1. Plot of the logical block address of each arriving IO request to its virtual time for the mobile trace used in [10]

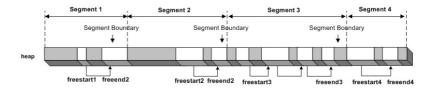

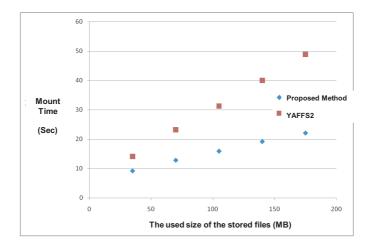

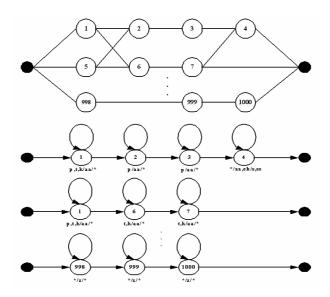

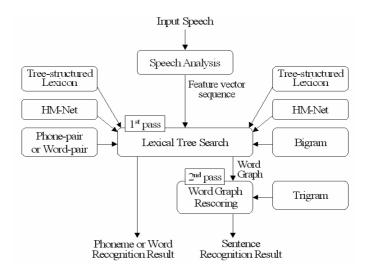

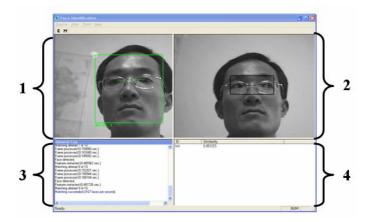

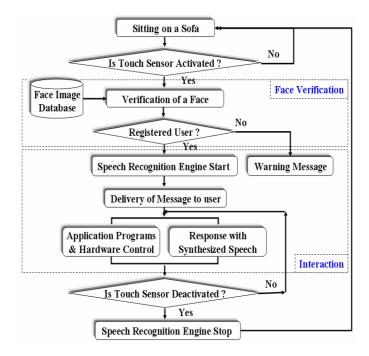

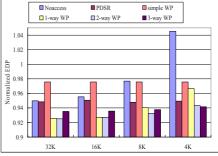

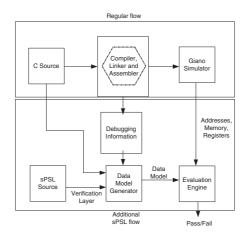

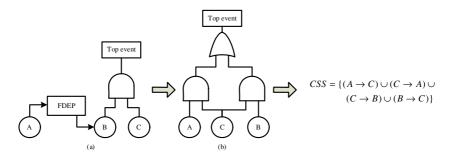

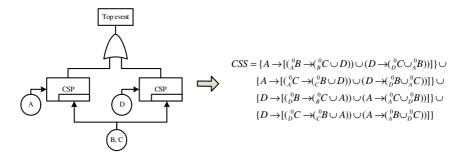

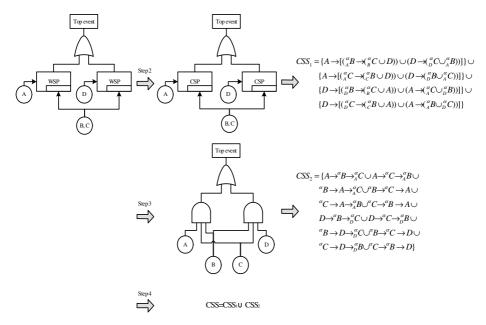

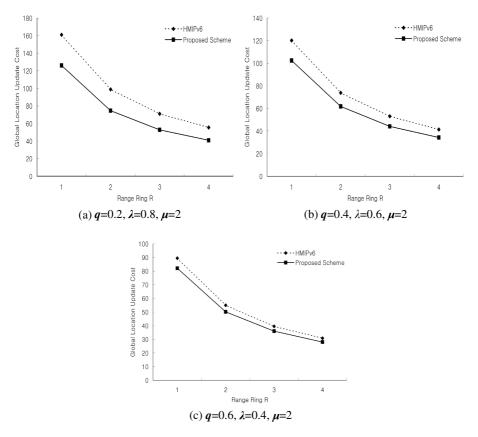

as well as in our heterogeneous storage system with a hard disk and a flash memory. As a first step towards a solution, we first tackle the design of WAC, our workload-aware cache replacement algorithm using different cost per block according to workload patterns similarly to the GreedyDual-Size algorithm.